|

|

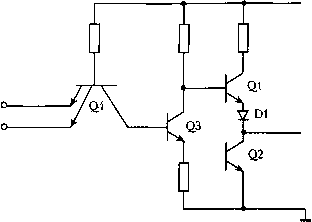

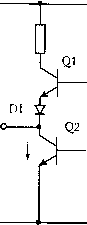

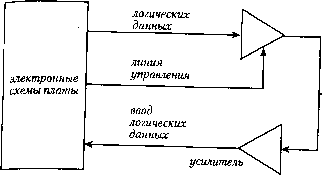

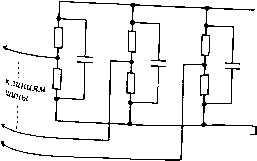

Главная страница Цифровые системы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [ 51 ] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] входы  о +V, о выход Рис. 8.7. Внутренняя структура логического элемента NAND на базе ТТЛ - транзисторы Q1, Q2 и диод D1 образуют выходную цепь-"вешалки" Если нагрузка присоединена к выходу "вешалки", ток будет проходить через транзисторы Q1 или Q2 в зависимости от логического состояния и от того, присоединена ли нагрузка к источнику (+У„„.) или к "земле". Если нагрузка присоединена между выходом и "землей", Q1 должен быть в состоянии пропустить ток нагрузки, когда выходное напряжение соответствует логической "1" (высокое). Наоборот, если нагрузка включена между источником и выходом, то Q2 должен потребить ток нагрузки, когда выход "низкий". В других состояниях не требуется ни питать нагрузку, ни потреблять ток. Рис. 8.7 также иллюстрирует типичную входную цепь ТТЛ. Чтобы ввести логический "О", входной контакт должен иметь напряжение 0-0.5 В относительно "земли", но для этого требуется, чтобы какой-либо ток протекал между входным контактом и "землей", т. е. вход ТТЛ эквивалентен нагрузке, присоединенной к ис точнику питания; выходной транзистор Q2 должен быть в состоянии отвести этот ток от каскадно соединенных входных цепей. Поэтому устройства ТТЛ также зывают логическими цепями с потреблением тока (current sinking logic). Типичн потребляемый ток составляет Е6 мА при напряжении питания -1-5 В. ВыхоД цепи ТТЛ обычно рассчитаны на управление не менее чем десятью №У.. ройствами ТТЛ, так что выходной транзистор Q2 должен пропускать ток по кр ней мере 16 мА. „псколькУ Две "вешалки" ни в коем случае не должны соединяться напрямую, пи если на одном выходе будет высокое напряжение, а на втором - низкое, то ц, питания окажется закороченным (рис. 8.8). Транзисторы могут быть повре а броски мощности - послужить источником шума и привести к ошибочной Р электронных устройств. ред- Другим типом выхода ТТЛ является открытый коллектор (open collector), ставляющий собой последовательное соединение выхода ТТЛ с транзистороМ.,, тер которого соединен с "землей", а коллектор используется как новый р,. (рис. 8.9 а). Когда транзистор проводит ток, выход имеет потенциал "земли гом состоянии уровень выхода теоретически бесконечен, поскольку выходной такт изолирован от "земли" импедансом. Чтобы при открытом транзисторе задать на е напряжение, соответствующее напряжению питания, предусмотрен нагру-."чяЫЙ резистор, подключенный к выходу (рис. 8.9 6). i D1  -О +V, Рис. 8.8. Соединение двух "вешалок", приводящее к короткому замыканию, - левый выход имеет логический уровень "1" (Q1 и D1 проводят), а правый выход имеет логический уровень "О" (Q1 заперт, Q2 проводит) ТТЛвход о -о выход ТГЛвход о- нагрузочный резистор -о выход тенци " открытым коллектором; а - Выходное напряжение либо равно по-зисто! земли", либо является неопределенным; б - применение согласующего ре-ческог "°-"Учения фиксированного выходного напряжения и в состоянии логи-o о ,ивсостоянии логической"!" Хемео" выходов типа открытого коллектора соединены вместе распределенного ИЛИ (wired OR). Уровень напряжения на линии высокий "лько то " Kwirea UK), ровень напряжения на линии высокий Чн ити "" транзисторы заперты, т. е. ни один не проводит ток. Когда "•ень выходов имеют низкий уровень, общая линия также имеет низкий )Хй, "распределенного ИЛИ" применяется для обмена информацией об- (, [Рактера, понятной всем устройствам, например, что все платы готовы к рабо-Чия "" "т задать на линии низкий потенциал, например, для опове- остальиых, что она еще не готова. Все платы следят за состоянием линии - Глава 8 достаточно одной плате "посадить" линию на низкий потенциал, как другие сп наружат это. Благодаря своей простоте схемы открытого коллектора и "распре ного ИЛИ" широко применялись в ранних конструкциях шин. • ~-1!;:ц,1 Щ . структура и принципы работы шин вывод лггния "распределенного ИЛИ" нагрузочный резистор Рис. 8.10. Пример соединения типа "распределенного ИЛИ". Если хотя бы один транзистор проводит, на общей линии "распределенного ИЛИ" устанавливается потенциал земли Схема "распределенного ИЛИ" при высоких скоростях работы чувствительна к паразитной емкости линии. Нагрузочный резистор R образует с распределенной емкостью линии С последовательный RC-контур. Из-за этого переход от низкого уровня к высокому замедляется и определяется величиной постоянной времени этого контура, при этом R нельзя уменьшить произвольно для снижения этой постоянной, поскольку большие токи перегрузят транзисторы интерфейса, а распределенная емкость линии С - величина постоянная. В схеме открытого коллектора также возникают проблемы, если в конфигурации "распределенного ИЛИ" проводит более чем один транзистор. Когда отключает!: транзистор, по которому протекала большая часть тока, возникает волна перенапр: жения, распространяющаяся по линии до тех пор, пока не начнет проводить слеДУ> щий транзистор. Это явление называется "всплеском распределенного ИЛИ ( 8,11) треть OR glitch"). Современные шины основаны на тристабильной логике (tristate logic) (рис- тьем С обшаС- и а- Два состояния схемы - это логические "высокий уровень" и "низкий уровень состояние называется "плавающим" или "высокоимпедансным", В этом тре стоянии цепи интерфейса не влияют на линии шины, но состояние линий со< ся внутренним схемам на платах. Тристабильиые схемы применяются главным образом для обмена данными ресации. Одна плата управляет шиной с помощью обычных сигналов высокого/,, кого уровня, а оста.дьные удерживают свои выходы в высокоимпедансном состо ,, одновременно получая сигналы с шины. Выходы тристабильных схем можно с пять вместе без всякого риска. Основным состоянием является высокоимпеда вход, и только после явного подтверждения схема тристабильного интерфе рейдет к одному из выходных состояний. Такое подтверждение дается то.яько когда плата получает право управлять шиной. усилитель  * кшине Рис. 8.11. Интерфейс на основе тристабильной логики В современных шинах комбинируется интерфейс на основе тристабильной логи-,:!д.м обмена данными и адресами и интерфейс "распределенного ИЛИ" для инди--адии готовности к приему и передаче данных, координации операций и посылки апросов на прерывания. В высокоскоростных шинах тристабильиые схемы исполь-потся также вместо схем "распределенного ИЛИ", чтобы преодолеть свойственный последним недостаток, связанный с временем нарастания сигнала. При высоких частотах, на которых работают шины, каждый проводник ведет :е6я как линия с распределенным импедансом. Как указывалось в описании мйств электрических проводников в разделе 4,5.2, характеристические импе-мсы всех присоединенных устройств и обоих концов каждой линии должны Wb согласованы, иначе будет происходить отражение сигналов. Если уровень раженных сигналов достаточно высок, они могут создать помехи нормальной хботе. избежание отражения сигналов на обоих концах шины устанавливаются спе-•иьные оконечные цепи {termination network) с импедансом, равным волновому педансу линии (рис. 8.12). Оконечные цепи демпфируют паразитные колебания, званные быстрыми переходными процессами в линии. Эти цепи либо монтируют-•чепосредственно на объединительной панели шины, либо устанавливаются на которые вставляются в разъемы на концах шины (рис. 8.6).  330 Ом 470 Ом 0.1 мкФ для каждой линии S.12.0 конечная цепь шины 8.2.4. Электрический интерфейс шины Проводники шины можно разделить на следующие группы: - линии адреса (адресная шина); - линии данных (шина данных); - линии управления - квитирование, прерывания, синхронизация; - линии питания; - резервные линии. По адресным линиям (address lines) передается адрес на шине источника или получателя данных. Стандартная разрядность адреса возросла с 16-20 бит в первоначальных разработках до 32-64 бит в современных системах. Каждая присоединенная п.дата оперирует в пределах определенного адресного диапазона - подмножества полного адресного пространства шины - и должна самостоятельно определять, когда адрес на шине принадлежит ее диапазону. По линиям данных (data lines) передается информация между адресуемыми объектами. Аналогично адресной шине, разрядность шины данных возросла от 8 до 32 или 64 бит. Линии управления (control lines) используются для передачи служебных сигналов, например типа операции (чтение/запись), индикации готовности посылать или принимать данные или запроса прерывания для специальной обработки одним из процессоров. Обычно одна из линий передает тактовые импульсы определенной частоты, используемые в качестве общего сигнала синхронизации. Большинство плат не имеют автономных источников питания и получают его от шины. Линии питания (power lines), как правило, находятся под напряжением ±5 В и ±12 В. Полюс источника питания и "земля" обычно присоединяются к нескольким контактам для того, чтобы равномерно распределить ток нагрузки установленных плат между несколькими проводниками. Резервные линии (spare lines) ни к чему не присоединяются; они предназначены для дополнительных функций в случае пересмотра стандарта шины. Кроме того, могут быть специально оставлены свободными для нужд пользователя. Не все типы линий обязательно присутствуют во всех стандартах шин. Р?*" ность адреса и данных может изменяться, количество линий квитирования зави от протокола, а способы поддержки прерываний отличаются для разных стандар шин. Некоторые линии шины работают при высоком уровне напряжения - в,. логическом уровне (active high), а некоторые при потенциале "земли" - низко ческом уровне (active low). Чтобы избежать путаницы, говорят, что линия лиоо вирована (asserted), либо сброшена (negated), независимо от того, относится л jjj вированное состояние к высокому или низкому логическому уровню. логический уровень линии указывается в справочной документации звездочк следующей за названием линии, или надчеркиванием названия, например или NACK. Активные линии, работающие на низком логическом уровне, ча.ст g2 5. Принципы работы шин дротокол (protocol) - это набор правил для координации обмена данными и вы-нения других операций на шине. Эти правила так же важны, как и назначение оводников, поскольку обеспечивают совместимость и возможность обмена информацией между соединенными платами. Любые операции шины должны быть точно ,пределены в части используемых линий и требуемой синхронизации. Для обеспечения совместимости с шиной и, соответственно, с другими присоединенными к шине (.тройствами плата должна подчиняться протоколу шины. Плата, которая в данный момент времени задает адрес на шине и операцию, ,оторая будет выполняться, называется ведущим устройством (bus master). Ведомое устройство (bus slave) - это устройство, к которому обращается ведущее и которое должно реагировать на его команды. Например, в операции передачи данных .между процессором и памятью процессор является ведущим, т. е. устанавливает адреса и указывает операцию - чтение или запись. Плата ОЗУ, являющаяся ведомой, опознает адреса и отвечает, считывая данные с шины или передавая их на шину. В некоторых системах ведущим может быть только одно устройство, в других - права ведущего устройства могут передаваться от одной платы к другой. Если ведущее устройство не выбрано однозначно, несколько плат могут пытаться одновременно получить доступ к шине, и тогда сочетание конфликтующих запросов может "запереть" шину - конкуренция за управление шиной (bus contention). Для решения этой проблемы применяются специальные арбитражные цепи. Шины могут быть синхронными и асинхронными. Синхронные шины (synchronous bus) работают в соответствии со специальным сигналом синхронизации - последовательность прямоугольных импульсов с частотой 10-20 МГц, которая генерируется одной из плат. Период задающего сигнала называется тактом иины (bus cycle). В шинах синхронного типа все операции должны выполняться соответствии с точным количеством тактов. Протокол асинхронной шины nchronous bus) предполагает, что очередная операция может начаться только г-да, когда завершена предыдущая. В шинах асинхронного типа отсутствует за-ющий генератор и для служебных протокольных сигналов и индикации готов-йтсГ """"У механизм квитирования (handshaking), для которого выделя-опре линии шины. В шинах синхронного типа готовность оыт,. тактовыми сигналами - на определенном такте все платы должны готовы к операции. -инхп рассмотренных типов шин имеет свои преимущества и недостатки. ""Редел"" шины проще, но выполнены на базе технологии, характерной для •Ртен*"""™ и имеют сравнительно небольшие возможности для усо- Чму °"ния. Асинхронный режим обладает большей гибкостью благодаря работающие с разной скоростью, могут быть установлены на Нол успешно работать вместе. Платы, выполненные по новейшей Ч аг обладающие высоким быстродействием, легко интегрируются с шп- или NACK. Активные линии, раоотаюшис ниоим jiui и нсиг.и™ jpw-, - д- "HaCHHV,--------- ----- - ..-.-xivu ип1С1Ь.ируЮ1иЯ с ШИ- ооены на схеме "распределенного ИЛИ", которая применяется, когда все плать 05 «хронного типа предыдущего поколения. Более сложная электроника, не- й,,..,. . и,,,полнению какой-либо опепаиии. - есди " Дя асинхронных шин, обычно не является ппепятстпирм.ппг 1Г Г\ ТГ т. ty- л г повременно должны быть готовы к выполнению какой-либо операции, - не готова к работе, она просто задает общей линии низкий потенциал, и оста/ платы могут распознать эту ситуацию. Аимая для асинхронных шин, обычно не является препятствием, поскольку кг, """ интегральных схем определяет достаточно низкие цены на интеп-"-Ные ---- устройства. [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [ 51 ] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] 0.0106 |