|

|

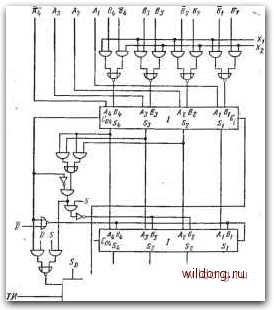

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [ 99 ] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] сумматоре. Коррекция результата производится во втором четырехразрядном сумматоре так же, как у описанных ранее параллельных сумматоров. Перенос Са записывается тактовым импульсом в /)-триггер), и прибавляется к двоичному коду следующей десятичной цифры, соответствующему декаде более высокого разряда. Схема на рис. 6.152 позволяет производить сложение или вычитание двоичных кодов десятичных цифр. Перед сложением О-триг-

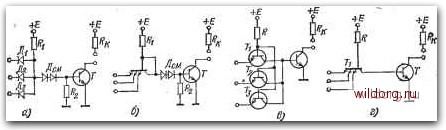

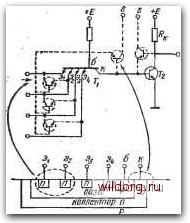

Рис. 6.152. Сложение или вычитание двоичных кодов десятичных цифр: / - четырехразрядный сумматор; - результат; / - сложение; IV - вычитание гер устанавливается асинхронным входом Sd в состояние Q=l, а перед вычитанием - асинхронным входом Rd в состояние Q=0. Вычитание основано на использовании единичных дополнений вычитаемых чисел. " В/)-триггер записывается: С=Со4-Ь (52-Ь5з)54. (,Прим. ред.). ГЛАВА 7 Интегральные цифровые схемы 7.1. ИНТЕГРАЛЬНЫЕ ЦИФРОВЫЕ СХЕМЫ ТТЛ Общая характеристика схем ТТЛ Интегральные цифровые схемы ТТЛ являются в настоящее время самыми быстродействующими схемами, в которых используются «асыщенные транзисторы. Главный элемент здесь - многоэмиттерный входной транзистор, для реализации которого необходима очень маленькая площадь на основиой кремниевой пластинке. Этот транзистор обеспечивает весьма быстрое заиирание всей схе- . мы, результатом чего является минимальная задержка при передаче сигнала от входа к выходу. Большим достоинством схем ТТЛ является возможность оптимального проектирования каждого интегрального компонента с учетом достижения наилучших свойств всей схемы. При большой скорости переключения монолитные интегральные схемы ТТЛ имеют хорошие показатели и с точки зрения мощности потерь, коэффициента объединения по входу, разветвления выхода л допустимого уровня помех. Схемы ТТЛ для малых перепадов сигналов ПРИНЦИП ПОСТРОЕНИЯ СХЕМ ТТЛ Схемы ТТЛ представляют собой, в принципе, следующий- этап развития схем ДТЛ, от которых они отличаются тем, что входные диоды заменены транзистором с несколькими эмиттерами. Рассмотрим сначала основные свойства схемы ДТЛ с дискретными элементами (рис. 7Ла). Эта схема позволяет добиться большого быстродействия с минимальными перепадами сигналов. Если на всех входах - уровень В, то диоды заперты и транзистор Т насыщен. Если на каком-либо входе - уровень Н, то транзистор Т закрыт; это состояние обес-  Рис. 7.1. а) Схема на дискретных элементах; б) пример схемы монолитного интегрального элемента ДТЛ; в) схема ТТЛ на дискретных элементах; г) монолитная интегральная схема ТТЛ печено смещением напряжения на диодах Дсм. Время переключения в открытое состояние увеличивается за счет времени восстановления входных диодов д1-д3. Однако значительно хуже условия переключения в закрытое состояние, если диоды Дсм имеют такие же свойства, что и входные. В этом случае избыточный заряд может быть отведен с базы транзистора Т только через резистор Ri На землю, поэтому время переключения в закрытое состояние сокращается путем уменьшения сопротивления резистора Ri. Но при этом одновременно уменьшается ток, необходимый для возбуждения транзистора до насыщения, а поэтому уменьшаются нагрузочная способность выхода и его коэффициент разветвления. Быстрое запирание транзистора Т может быть ойеспе-чеио при достаточно большом сопротивлении резистора Rx только тогда, когда яспользуются диоды Дек, в которых во время насыщенного состояния тран-зястора Т иакапливается достаточно большой заряд. В этом случае ббльшая часть заряда отводится на землю при запирании транзистора через малое сопротивление днодов Дсм и входных диодов. На рис. 7.16 представлена схема монолитной интегральной схемы ДТЛ. Вместо входных диодов использована транзисторная структура с соединением базы с коллектором, что уменьшает емкость входных диодов. Однако быстродействие опять ограничено диода.ми смещения Дсм- Решеиие указанных проблем обеспечивает схема на рис. 7.1в, в которой вместо входных диодов использованы отдельные транзисторы Ti-Тг. Переходы эмиттер-база этих транзисторов соответствуют входным диодам д1-Да, а включенньге параллельно переходы коллектор-база соответствуют диодам смещения Дом. Если на всех входах - уровень В, то параллельно включенные переходы коллектор-база имеют малое сопротивление и через них течет ток от резистора R на базу транзистора Т, который насыщается. Если на каком-либо входе - уровень Н, то ток с резистора R течет на этот вход и напряжение на базе транзистора Т падает до такого низкого значения, при котором этот транзистор надежно заперт. Главным достоинством этой схемы с точки зрения быстродействия является быстрее рассасывание избыточного заряда базы транзистора Т. При его запирании заряд рассасывается через малое сопротивление между коллектором и эмиттером входного транзистора, на входе которого напряжение изменилось с уровня В на Н. Тем же путем течет остаточный ток базы запертого транзистора Т. Поэтому в схеме нет необходимости в резисторе R, что является также достоинством. Эта схема является типичным примером нового принципа, особенно пригодного для монолитных интеграл.ъных схем. Схемы на дискретных элементах дороги из-за оравнительно высокой цены отдельных транзисторов. В монолитной интегральной схеме цена транзистора не имеет такого значения, кроме того, миого-эмиттерный транзистор, который заменяет отдельные входные транзисторы, обеспечивает дальнейшее улучшение и упрощение работы. Очень простая схема монолитного интегрального элемента ТТЛ для небольших перепадов сигналов показана на р.ис. 7.1г. В многоэмит-терном транзисторе в процессе переключения не происходят накопление и рассасывание заряда в базе. Заряд, иакопленный в базе во время работы схемы, просто перемещается в области базы, соответствующие тем или иным э.миттерам. Благодаря этому увеличивается быстродействие схемы. Однако в схеме на рис. 7.1г также имеются некоторые сложности. Одна из них не .имеет аналогии в схемах на дискретных элементах.  Основная кремниевая ппастита (поЗложиав) Рис. 72. Монолитная интегральная схема ТТЛ с паразитными транзисторами [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [ 99 ] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0242 |