|

|

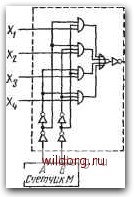

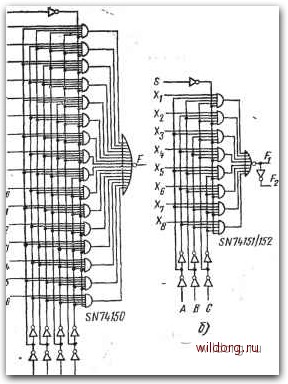

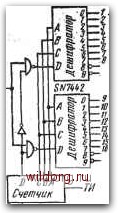

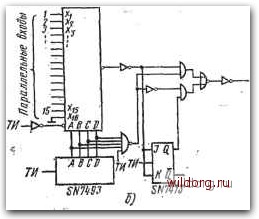

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [ 95 ] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] -I I-io J-l n n r-a Hi тшшшшшишпмг? £IZlU0lS9L9SiS2 I J-LJ-LJ- TJTJ-TJTJ-LTLr И1 i r a. a тлплллшшллллг sill и 01 в a L a s I £ г i Г- u-u-u- J-U-U-LJ~ J-L I-L J" -a и "1 r~ ~L r ~t Г -Г-~\ Г- -l n J-L -innnruinnnnj- 01 S 8 L 9 S Ь. £1 I епизщ luuanji -Пффеа)1 Z9 -ifpBi эинвьноно 6 10. ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЕ И ПОСЛЕДОВАТЕЛЬНО-ПАРАЛЛЕЛЬНОЕ ПРЕОБРАЗОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ Принцип представлен на рис. 6.138. На четыре входа - Xi-Xi, - информация подается параллельно. Двухразрядный счетчик с выходами А, В адресует параллельные входы в последовательности XiX%X%XiJCx и т. д., и в той же последовательности  =фН»-Х I А В Счетчиво АВ В) АВАВ -t i AS... Рис. 6.138. Передача информации: я) параллельно-последовательная; б) последовательно-параллельная; е) временные диаграммы счетчиков значения отдельных входов передаются на общий выход F. На-иример, параллельные информационные сигналы Xi=:l, Xz=0, Хз=1, 4=1 передаются с выхода F последовательно, как Х1Х2ХзХ4=1011. Схема на рис. 6.138а, осуществляющая параллельно-последовательное преобразование, обычно называется мультиплексной. Демультиплексная схема на рис. 6.1386, преобразующая последовательную информацию в параллельную, работает подобным образом. Двухразрядный счетчик D, имеющий выходы Л, В, работает синхронно со счетчиком М, имеющим мультиплексное включение, и последовательно адресует выходы Xi- -Xi, на которых последовательно появляется исходная информация Xi=\, Х2=0, Хз=1, Xi=l. Временные характеристики счетчиков показаны на рис. 6.138в. Этот принцип выгоден для передачи информации между удаленными блоками цифровой системы, так как он очень прост и экономичен. Время передачи, конечно, больше, чем при параллельной передаче информации, и оно возрастает с увеличением числа передаваемых бит. Так как мультиплексные схемы имеют широкое применение, то они выполняются также в виде полностью интегральных монолитных схем с разным числом входов. На рис. 6.139 приведены схемы таких интегральных мультиплексных  ABCD Puc. 6.139. Монолитные интегральные мультиплексные схемы: а) с 16 входами; б) с 8 входами ....., к- % \A8CB ПослеВвЙО! тельный , АВСВ Счетчик  sm93  ВоследоВатель-ный ШвО Рис. 6.140. а) Пример схемы на мультиплексном интегральном элементе с 16 входами и интегральных счетчиках и дешифраторах; б) (Параллельно-последовательная передача с генератором бит четности [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [ 95 ] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0094 |