|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [ 8 ] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] работает в насыщенном режиме, положительное напряжение помехи может влиять на ее работу двояко: а) схема В так насыщена, что помехи не оказывают влияния на входные рабочие условия и передаются прямо на выход схемы В;

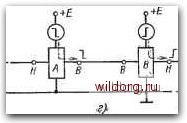

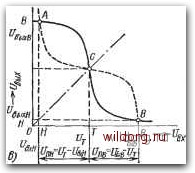

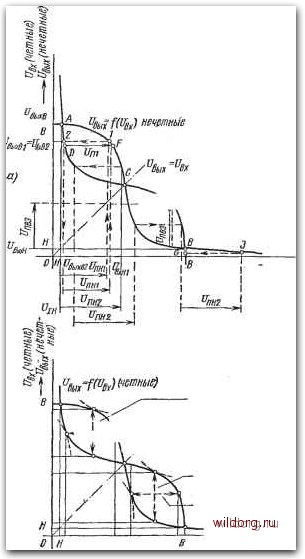

Рис. 1.19. Помехи инвертирующих схем с усилением: а) на входах; б) на заземляющих соединениях; в) на общей шиие питания; е) на отдельных проводах, подводящих питание б) схема В насыщена мало, помехи уменьшают входной уровень В до такой величины, при которой схема В перестает работать в Области насыщения, результатом чего явится положительное паразитное изменение напряжения на выходе схемы, как и в случае «а». В качестве примера на рис. 1.19в показаны помехи, возникающие на общей шине питания. Отрицательное паразитное изменение может передаваться на выход схемы А и уменьшать уровень В на входе схемы В. На рис. 1.19г дан пример помех, возншсающих на проводах, подводящих напряжение питания к схемам А я В, подключенным к разным источникам напряжения. Влияние помех на проводах питания схемы А подобно случаю на рис. 1.19в. У схемы В, i которая находится в насыщенном состоянии, на выходе появится помеха, уменьшенная пропорционально соответствующим сопротивлениям. Так как со-: противление выходного насыщенного транзистора очень мало, то влияние такой помехи незначительно. Очевидно, степень влияния помех зависит от типа используемых схем. Из предложенных примеров вытекает, что все помехи можно отнести к входу схемы, что позволяет анализировать влияние помех по передаточным характеристикам схемы £/вых=?ГtBiJ. Допустимые статические помехи цифровых схем Существуют два предельных случая -влияния помех на работу цепочки цифровых схем. В первом случае помехи действуют в самом неблагоприятном направлении только яа одну схему цепочки. В другом случае эти помехи воздействуют на каждую схему цепочки. В то время как первый случай слишком оптимистический, второй - слишком пессимистический, ио более реальный, так как с точки зрения нормальной работы цифровой системы лучше предполагать и учитывать ва1риант, когда помехи действуют в большей части схем цепочки. Поэтому .максимально допустимый диапазон помех цифровых схем должен рассматриваться прежде всего исходя из второго случая. Влияние помех на цепочку цифровых схем Рассмотрим цепочку инвертирующих схем на рис. 1.20а. На входах всех нечетных схем - ], 3, б я т. д. - имеется уровень Н, на входах четных схем - 2, 4, 6 я т. д.-уровень В. Помехи имеют место только в схеме 3. Предполагая, что передаточные характеристики всех схем цепочки одинаковы (рис. -1 I- -г.-  Рис. 1.20. а) Цепочка инвертирующих схем с усилением и с помехами на уровне Н на входе одной из схем; б) помехи на уровне В одной схемы; в) максимально допустимые значения сигналов помех 1.20в), можно сказать, что установившемуся рабочему режиму всех нечетных схем соответствует рабочая точка А, а четных -точка В. Напряжение на входе схемы 3 может увеличиваться за счет сигнала помех it/п.н только на такую величину, при которой уровни последующих схем стремятся к первоначальным рабочим точкам. Как было сказано в § 1.6, критерием является величина порогового напряжения Ub%- То же самое справедливо для схемы 3(рис. 1.206), на которую при входном уровне В воздействует отрицательное напряжение помехи Un.B. Так как в представленном примере предполагаем £/вхн=/выхн и /вхв = /выхв, то максимально допустимые значения сигналов помех будут: ПНмакс вых Н, ПВмакс - выхВ - fT • (1.6) (1.7) Предположим теперь, что помехи имеют место на уровне Н каждой нечетной схемы. Установившимся режимам работы цепочки схем при отсутствии помех на рис. 1.21а соответствуют рабочие точки А я В. Если на входах всех нечетных схем появится положительный сигнал помех с а.мллнгудой t/n.Hi, то входное напряжение схемы 1 возрастет до величины t/BxHi=t/BxH-ft/ii.Hi, которой на передаточной характеристике соответствуют новая рабочая точка 1 и выходное напряжение £/выхВ1. Но выходное напряжение £/выхВ1 является одновременно входным напряжением t/exBa схемы 2, которому на передаточиой характеристике соответствуют рабочая точка 2 и выходное напряжение {/выхвг. Поэтому на входе схемы 3 будет напряжение !£/в1Нз=/выхН2-+-£/п.н1. Таким образом можно показать, что уровни нечетных схем сходятся в рабочую точку F, а уровни четных схем - в рабочую точку D, причем расстояние между обеими точками равно величине напряжения помех f)n.Hi. Если же- величина напряжения помех увеличится и будет равна t/n.Hz, то уровни нечетных схем стремятся к рабочей точке G, уровни четных схем - к рабочей точке /, и состояние схем в цепочке изменится. Аналогичные результаты будут получены в предположении наличия помех на уровне В каждой четной схемы. Максимально допустимые значения напряжения помех зависят от формы петли, образуемой передаточными характеристиками (рис. 1.216). Достаточно рассмотреть одну петлю, так как для инвертирующих схем обе петли симметричны. Для того чтобы не произошло изменения состояния в цепочке схем, помехи на уровне Н только четных или нечетных схем не должны быть больше, чем максимальная ширина верхней петли в направлении осн Увх.снечетн), а помехи на уровне В только четных или нечетных схем не должны превышать максимальной ширины верхней петли (направление оси £/в1.(четв)}. Самый сложный случай-искажение входного уровня всех схем цепочки (рис. 1.22с). Величины сигналов /п.н н Vn.B могут отличаться друг от друга, но самому тяжелому случаю соответствуют одинаковые напряжения Un.ti = 2 чт>-  « - ТТпв Vgfнечетные) UgiJvemHiie) максимально допустимые итатепия уровня В четных схем "Г --л . максимально допуотимыв / искажения уровня П нечетных схем максимально допустимые искажения уровня П четных схем максимально допустимые искажения уровня В нечетных схем -UgJ нечетные) /четные) Рис. 1.21. с) Рабочие условия при наличии помех на уровне Н каждой нечетной схемы или при наличии помех на уровне В каждой четной схемы цепочки инвертирующих схем с усилением; б) максимально допустимые значения сиг-палов помех [0] [1] [2] [3] [4] [5] [6] [7] [ 8 ] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0136 |

||||||||||||||||||||||||