|

|

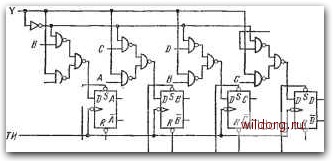

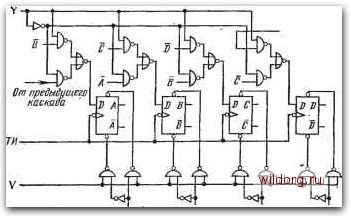

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [ 89 ] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] ется в регистр независимо от его состояния по команде /i=/2=l (одновременно); в) информация и ее дополнение передаются из регистра внешним цепям по команде 11=1, или 2=1, или Vi=V2=l (одновременно). Все эти возможности управления расширяют область применения сдвиговых регистров. Они могут быть использованы полностью или частично в зависимости от назначения регистра. Некоторые интегральные триггеры не имеют асинхронных управляющих входов R и S. Поэтому для обеспечения параллельного ввода информации в такие схемы необходима добавочная логика. На рис. 6.118а схема с логикой - в базисе И-НЕ/И-НЕ, flocjieSa-йателшщ-  Параллельный ШО OA- г-О В - г-В С - г-О Г - ,B~-t .Последовательный Шов Параллельный В Вод Рис. 6.118. Схемы сдвиговых регистров: а) с логическими элементами И-НЕ/И-НЕ; б) с коллекторной логикой И-НЕ для параллельной записи информации а в схеме на рис. 6.1186 использованы элементы И-НЕ с объединенными выходами. Информация записывается в регистр параллельно по команде V-6. Как уже было сказано, есть регистры, осуществляющие сдвиг Информации вправо (это наиболее частый случай), и регистры, производящие сдвиг влево. А иногда регистр должен иметь возможность сдвига информации в обоих направлениях. Схема тако-272 го регистра с логикой И-НЕ и D-триггерами показана на рис. 6.119. В таких реверсивных регистрах очень выгодно использовать триггеры, так как у них только один управляющий вход (очевидно, что при использовании -триггеров был бы необхо- От следующего каскада  От предыдущего каскада Параллемит ВШ Рис. 6.119. Схема реверсивного сдвигового регистра Отследующего каскада  Параллельтш ввод Рис. 6.120. Схема реверсивного сдвигового регистра ДИМ двойной объем логической схемы). При У=1 информация сдвигается вправо, при У=0 - влево. Параллельная запись в регистр независимо от его состояния возможна по команде V-\. На рис. 6.120 представлена схема, имеющая такие же функциональные возможности, но комбинационная логика выполнена на элементах И/ИЛИ-НЕ и И-НЕ. Условия правильности работы сдвиговых регистров Чаще всего в сдвиговых регистрах используются триггеры типов D и JK, а в полностью интегральных сдвиговых регистрах и iS-триггеры. Триггеры могут управляться одним фронтом тактовых импульсов или Обоими фронтами одновременно. При использовании триггеров, управляемых одним фронтом его крутизна может быть достаточной. Как уже объяснялось выше, последующее состояние синхронных триггеров зависит и от их предыдущего состояния, однако при переключении триггеров в новое состояние информация о предыдущем должна быть заменена новой информацией. Интегральные триггеры типов D и JK, управляемые одним фронтом, обычно имеют связи по постоянному напряжению, а триггеры наиболее часто используемых типов реагируют на положительное изменение тактовых импульсов. У этих триггеров время хранения информации о предыдущем состоянии может быть очень малым, равным задержке одного или двух базовых элементов, и при медленном изменении тактового импульса эта информация может совершенно исчезнуть или принять неопределенное значение. Результатом явится неверное следующее состояние триггера. Предположим, что в момент t=n состояние регистра ЛБС/)=1101. Если на входе регистра информация О, то состояние регистра в момент t=n-\-\ должно быть ЛБС/) = ОПО. Однако при медленном нарастании тактового импульса может иметь место случай, когда какой-то триггер запишет информацию предыдущего триггера перед общим сдвигом. Например, триггер С запишет информацию 1, в результате чего состояние регистра изменится на ABCD=\\\\, и после тактового импульса регистр будет в ошибочном состоянии ЛБС/)==0111. Поэтому для обеспечения надежной работы сдвигового регистра нужно использовать тактовые импульсы, имеющие достаточную, крутизну активного фронта. Если это нельзя обеспечить, то должны быть использованы триггеры, управляемые обоими фронтами тактовых импульсов. Синхронные сдвиговые регистры с обративши связями Основные понятия На базе простых схем, главной задачей которых был только сдвиг информации, постепенно возникло много схем с многосторонними функциональными возможностями. При введении соответствующих обратных связей сдвиговые регистры могут работать как счетчики, генераторы кодов; соответствующая логика позволяет использовать их для преобразования кодов, для умножения и деления двоичных чисел и т. п. Важен факт, что все эти функции могут быть реализованы с помощью сравнительно простой логической схемы. 274 [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [ 89 ] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0118 |