|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [ 73 ] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] к ти-J щ

Рис. 6.68. а) Схема триггера на рис. 6.54; б) полная карта функций Vi, Уг в зависимости от всех управляющих входов /, К, ТИ, (/?D, Sd УСЛОВНЫЕ ОБОЗНАЧЕНИЯ СИНХРОННЫХ ТРИГГЕРОВ При использовании различных типов синхронных триггеров в одной системе целесообразно различать их символически не только по функциям подготовительных входов, но и по реакции триггера на тактовые импульсы. Примеры таких условных обозначений приведены па рис, 6.69. Обозначение входа тактовых ям-пульсов на рис. 6.69 справедливо для триггеров, управляемых од-

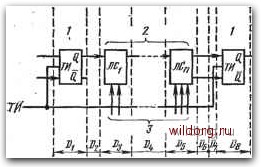

Активный фрон/п Активный фронт MS а) Bli АктиБный фронт Антиёшй М-В В-~Р Рис. 6.69. Условные обозначения синхронных триггеров: и) управляемых одним фронтом тактового импульса; б) двумя фронтами тактового импульса ним фронтом, а на рис. 6.696 - для триггеров, управляемых двумя фронтами. Конъюнктивные и дизъюнктивные функции подготовительных входов можно выразить с помощью обычно используемых символов внутри самого символа триггера. Быстродействие последовательностных систем на триггерах Быстродействие последовательностной системы на триггерах зависит не только от быстродействия самих триггеров. В принципе, на быстродействие системы оказывают влияние следующие факторы. Организация системы. Различают системы параллельные, последовательно-параллельные и последовательные. Наиболее быстродействующие системы - параллельные, наименее - последовательные, чаще всего используются последовательно-параллельные системы. Способ управления, В зависимости от способа управления системы делятся на синхронные, асинхронные и комбинированные, в которых некоторые блоки работают синхронно, а другие - асинхронно. Асинхронные системы обладают большим быстродействием, но их реализация более сложная, а работа менее наглядна, чем у синхронных систем. Задержка сигналов в базовых схемах. Этот фактор имеет наибольшее влияние на быстродействие системы, однако он зависит от множества других факторов. На величину задержки влияют: разветвление входов и выходов, колебания температуры и напряжения питания и прежде всего емкостные нагрузки входов и выходов. Кроме собственных емкостей используемых базовых элементов, должны быть учтены емкости печатных соединений и всех остальных подключенных проводников. Задержка сигналов на соединительных линиях С точки зрения ограничения быстродействия системы за счет задержки сигнала нельзя считать первостепенным фактором, например, максимальную частоту тактовых импульсов, специфицированную для триггеров соответствующей серии цифровых элементов. У логических схем должно быть достаточно времени для завершения требуемых операций до того, как под действием так-й оч 225 товых импульсов результаты этих операций будут записаны в триггер; Наглядный пример приведен на рис. 6.70. Допустим, что на триггер А воздействует отрицательное изменение тактового импульса ТМ и после задержки Dj на выходе Q появляется сигнал 1.  Рис. 6.70. Задержка сигнала в последовательной системе: / - триггер; 2 - комбинационная логическая схема; 3 - информация от других логических схем После задержки D2 этот сигнал появляется на входе логинес-кой схемы ЛСь Сигнал на выходе этой схемы появится с задержкой Dz и т. д. Сигнал проходит далее по проводам, через логические cxejMbi, усилители и т. п. до следующего триггера В. Через определенное время Dj, в течение которого информация должна быть на управляющих входах триггера, появится новая информация, причем с задержкой Dg. Ясно, что интервал времени между отрицательными изменениями двух следующих друг за другом тактовых импульсов не должен быть короче, чем полная задержка DDi+Dz+Ds+Di+Ds+De+Dj. Поэтому максимально допустимая частота тактовых импульсов равна f=l/D и не имеет непосредственного отнощения к максимальной частоте переключения самого триггера. Условия правильной работы триггеров Рассмотрим схему на рис. 6.71а с передачей информации с выхода триггера А на входы триггера В. Предположим, что это У/С-триггеры, работающие на принципе главной и вспомогательной памяти, выход которых изменяется под действием отрицательного изменения тактового импульса. Используя временную диаграмму на рис. 6.71, рассмотрим теперь принцип работы схемы. В момент времени о, в начале тактового импульса, управляющие входы триггера А находятся в состоянии Ja=Ka=1, триггера В-Ув = 0; Кв=1. В момент тактовый импульс заканчивается, а в момент tz с определенной задержкой состояние выхода триггера А меняется на значение Qa = = 1. После некоторой задержки в логической схеме в момент 4 изменится состояние входа /в триггера В на значение /в=1. С точки зрения непосредственного воздействия фронта и спада так- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [ 73 ] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0137 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||