|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [ 71 ] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] отрицательном изменении тактового импульса с ТИ=:1 на ТИ = 0 выход F блокирует работу цепи D, но на выходе С в связи с разрядом диода Ml происходит изменение со значения С=1 на С=0, и после того как будет достигнуто определенное пороговое напряжение, главная память перейдет в состояние Q=l. Этот тип триггера имеет много преимуществ. Он довольно прост, в требуемое исходное состояние достаточно установить только главную память, несложно также увеличить число управляющих входов. В модификации схемы на рис. 6.606 функциональные возможности улучшены благодаря включению входных цепей типа И-ИЛИ. Накопление и рассасывание зарядов диодов можно осуществить так, что они будут происходить через небольшие сопротивления, поэтому эти триггеры могут работать при очень высоких частотах переключения с тактовыми импульсами, имеющими минимальную длительность-10 НС. Но данный принцип кратковременной памяти никак не ограничивает максимальную длительность тактовых импульсов, поэтому такие триггеры могут работать и при очень низких частотах переключения. Единственным условием является необходимость обеспечить определенную максимальную длительность управляющего фронта тактового импульса. Следующим преимуществом является нечувствительность триггера к внешним сигналам помех при Т-И=0 и при ТИ = 1. Принцип действия этих триггеров напоминает в некоторой степени работу триггеров с главной и вспомогательной памятью. Обратим внимание на то, что при достаточно большой длительности тактового импульса ТИ = 1 изменения состояния входов J и К могут оказать влияние на результирующее состояние триггера. Однако эти изменения проявляются не сразу, как у других типов триггеров, а после некоторой задержки, зависящей от постоянной времени кратковременной памяти. Обычно эта память проектируется так, чтобы накопление происходило быстрее, чем рассасывание, поэтому изменение состояния входов со значения О на 1 распознается быстрее, чем изменение с 1 на 0. С точки зрения асинх1ронного режима работы эти триггеры имеют очень важное свойство. Если во время действия ТИ=1 сигналы на входах J и К изменятся на значения С=00, то после действия тактового импульса состояние триггера не изменится. • Синхронные (-триггеры, управляемые одним фронтом тактового импульса Схема на рис. 6.61 состоит из элементов И-НЕ и реагирует на изменение тактового импульса со значения ТИ = 0 на ТИ = 1. Прямые (асинхронные) входы Rd и Sd оказывают влияние только на состояние выходной памяти. Из функциональной карты на -рис. 6.61 ясно, что блокирование входов во время действия тактового импульса ТИ = 1 недостаточно эффективно. При состоянии входов С=00 или (=01 состояние выхода Q=0 может измениться при положительном изменении на входе /, а при состоянии 218  ж ти=с 00 т 71 1о\10 11 01 оо\ооо1 и т 10 11 01 00 тштттшштаашшшшяи шшштшшшшштяеиаии 011 010 \ 110 I : / ioi\ lOO\iii\in\iiAiiAm\iii\iii\iii\ I I I I I I I I Рис. 6.61. а) Синхронный /УС-триггер, управляемый одним фронтом тактового импульса; б) карта функций Yi, Уг, Уз н карта переходов С = 11 ИЛИ С = 10 состояние выхода Q = 1 может быть изменено положительным изменением на входе К. Этот факт должен быть учтен при использовании триггера в счетчиках и других схемах. а) тя- П7 X X т-0 I ТИЧ , ти=о I тй=1 \ 00 01 11 10 \ 10 11 01 00 \оО 01 11 10 110 11 01 00 : ООО 001 011 010 Ф 110 101 W0

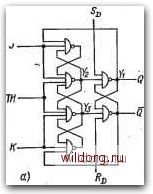

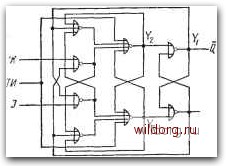

Рис. 6.62. а) Синхронный Ж-триггер, нечувствительный к помехам; б) карта функций Уи Уг, Уз и карта переходов  Этого недостатка лишен (-триггер на рис. 6.62, состоящий из элементов ИЛИ-НЕ. Как вытекает из функциональной карты на рис. 6.62, сигналы на входах J а К могут изменяться не только зпри ТИ = 0, но и при ТИ=1 и не оказывают при этом влиянияна зыход Q. Поэтому триггер почти нечувствителен к внешним помехам, которые могут воздействовать только в течение очень короткого времени, соответствующего изменению тактового "импульса со значения ТИ=0 на ТИ=11. По этой же причине триггер пригоден для асинхронной работы. Напри-- мер, асинхронные счетчики на этих триггерах можно составлять, используя те же систематические методы, что и для синхронных счетчиков. JK-триггер на рис. 6.63, имеющий упрощенное исполнение, обладает теми же свойствами, (-триггер на рис. 6.64 также реагирует на изменение тактового импульса с ТИ = 0 на ТИ=1. Асинхронными входами Rd и Sd триггер может быть установлен в нужное исходное состояние только при ТИ = 0. npHiSD = 0 и/?в= 1 будет Q = l; при Sd-1 и Rd= = 0 будет Q = 0. Если оба входа активны одновременно, т. е. Sd=0, Re=0, то оба выхода триггера перейдут в состояние 0. То же самое справедливо, если активен вход Rd илн Sd при ТИ=1. Большое число входов обеспечивает многостороннее использование триггера с минимальным количеством добавочных цепей. На выходах входных конъюнкторов активные (сигналы могут появиться только тогда, когда /i=l, /2=1, /* = 0, /(i = l, /(2=!, К*=0. Из •функциональной карты на рис. 6.64 вытекает, что триггер имеет .совершенноеблокированиевходов при ТИ=1. При ТИ = 0 изменение состояния входов J w. К может оказать влияние на внутреннее состояние триггера, однако состояние его выходов не изменится. В представленных схемах входы J и К должны блокироваться перед изменением состояния выходов триггеров. Рис. 6.63. Упрощенная схема синхронного /С-триггера, имеющего те же свойства, что и триггер на рнс. 6.62 Синхронные £)-триггеры Эти триггеры тоже могут управляться двумя фронтами или •одним фронтом тактового импульса. В интегральной технике создаются только D-триггеры, управляемые одним фронтом. На рис. 6.65 представлена схема D-триг-тера на базовых элементах ИЛИ-НЕ. Его работа понятна из функциональной карты на рис. 6.65. У данного триггера состоя- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [ 71 ] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0111 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||