|

|

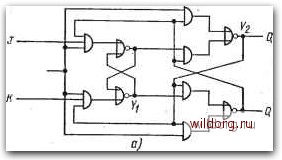

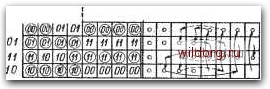

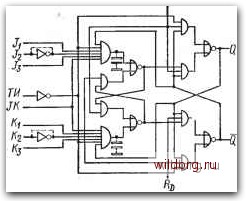

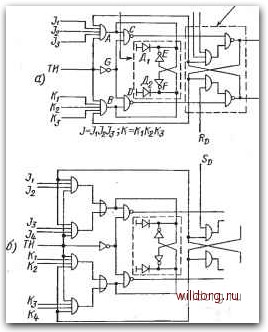

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [ 70 ] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] значения О на 1 прежде всего блокируются входы J и К, а потом следует передача информации из главной памяти во вспомогаг тельную. Функцию триггера отражает карта на рис. 6.566, из которой видно также влияние на работу триггера изменения состоя-  у,у\00 01 11 10 00 ти=1 ти=о ГИ=1 10 11 01 00\00 01 11 10 10 11 01 00 Рис. 6.57. а) Та же схема, что на рис. 6.56, но иа входах JK имеются инверторы; б) карта функций YiYz и карта переходов  У2=Угт1У2-У2ЩТН б] ния входов / и /с во время действия тактового импульса ТИ=0, Схема на рис. 6.57а отличается только наличием инверторов на входах J и К- В данном случае на входах J и К имеются активные сигналы. При /=0, К=1 триггер переключается в ак-тивное состояние: Q=l; при /=1, К=0 он переключается в исходное состояние: Q=0. Если на обоих входах постоянно присутствуют сигналы (=00, то состояние выхода Q изменяется после каждого тактового импульса. При C=ill триггер остается в состоянии Q=0 или Q= 1. Свойствами обеих разнообразных схем обладает триггер на рис. 6.58. Большое число управляющих входов и их функциональные комбинации обеспечивают многостороннее исполь-  Рис. 6.58. Синхронный Ж-триггер с инвертированием тактовых импульсов и с иеннверсными и инверсными входами Ж зование триггера с минимальным числом внешних добавочных цепей комбинационной логики. Входы /i, /3, Ки Ks и объединенный вход JK активны при сигналах.!, входы /2 и К2 активны при сигналах 0. •При исключении входных инверторов (на рис. 6.58 показано пунктиром) все входы могут быть одного функционального типа. Асинхронные входы Sd и Rd активны при сигнале О, они устанавливают триггер в нужное состояние независимо от состояния входов /, К входа тактовых импульсов. Конденсаторы, показанные пунктиром на выходах входных ключей, ограничивают влияние взаимно-то временного сдвига тактовых импульсов (см. ниже). Однако их -использование уменьшает максимальную частоту переключения триггера. Влияние на работу триггера изменений управляющих сигналов на входах JK во время действия тактового импульса вытекает из функциональных карт на рис. 6.56 и 6.57. Синхронные JK-триггеры с полупроводниковой и емкостной кратковременной памятью. При создании таких триггеров для Нрттфеттая Гмшш ттть пашшь ги,-J,- ,£) ти- If,- с ПраткоВрдметая пашть Главная память  Рис. 6.59. Синхронные /С-триггеры: а, б) с полупроводниковой кратковре-менцрй памятью; в) с емкостной кратковременной пащтью, Рис. 6.60. Примеры схем синхронных /Д-триггеров с полупроводниковой кратковременной памятью: а) с конъюнктивными входами /, К\ б) с входами J, К в функции И/ИЛИ кратковременной записи информации в виде зарядов можно использовать вспомогательные запоминающие устройства. Примерьв упрощенных схем показаны на рис. 6.59. Рассмотрим сначала; принцип действия схемы с полупроводниковой кратковременной; памятью. Если ТИ=0, то блокируется работа входов J, К и блокируются также передающие ключи между временной и главной памятью, так как на одном выходе кратковременной памяти нет-сигнала 1. После изменения тактового импульса со значения ТИ=0* на ТИ = 1 уровнем тактового импульса ТИ=1 блокируются передающие ключи, поэтому не может быть осуществлено воздействие-на главную память, и входная информация в зависимости от состояния входов записывается в виде заряда в кратковременную-память. В течение всей длительности та[ктового импульса ТИ=:1 входы соединены с кратковременной памятью, т. е. перед началом изменения состояния тактового импульса на одном из выходов*, кратковременной памяти есть сигнал 1, подготавливающий к от-рытию один из подключенных ключей. При изменении тактового» импульса со значения ТИ=1 на ТИ = 0 изменится и состояние* этого передающего ключа и при определенном пороговом уровне-сигнала он окажет влияние на состояние выходной памяти. Однако-информация с выходов главной памяти появится на входах только» в тот момент, когда воздействие входов уже блокировано и их: связь с кратковременной памятью нарушена. В несложной схеме на рис. 6.59в функцию кратковременной? памяти выполняют конденсаторы. Предположим, что Q = 0, /= =К=1. При ТИ.=0 блокируются входы /, К, причем ясно, что Л = 1 и В=1. А так как Q = 0 и Q=l, то после положительного» изменения тактового импульса с ТИ = 0 на ТИ.= 1 изменится только состояние выхода Л.со значения Л = 1 на Л = 0. Это состояние будет записано в подключенной кратковременной памяти. При отрицательном изменении тактового импульса со значения ТИ=1 на ТИ=0 блокируются входы, заряд кратковременной памяти воздействует на подсоединенный инвертор, под действием сигнала с выхода которого главная память перейдет в состояние Q = l. Запоминающие устройства на полупроводниковых элементах: для кратковременной записи информации в виде зарядов позволяют создать быстродействующие триггеры с частотой переключения порядка десятков мегагерц. Типичные схемы таких триггеров, приведены на рис. 6.60. Кратковременную память образуют диоды, с накоплением заряда Ди Дг и два накрест соединенных инвертора - EF. Предположим, например, что триггер на рис. 6.60а находится в состоянии Q-=0, J=K=1 и ТИ=0. Ясно, что в этом случае-Л = В = 0 и C=D=G=il, входы блокированы и нельзя воздействовать ни на кратковременную, ни на главную память. После положительного изменения тактового импульса с О на 1 изменится только состояние выхода Л (на значение Л = 1), которое будет зарегистрировано диодом В результате этого выходы инверторов-кратковременной памяти перейдут в состояние F=0 и Е=\. При [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [ 70 ] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0093 |