|

|

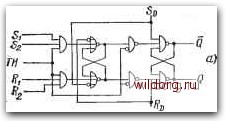

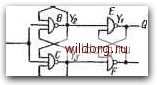

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [ 68 ] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] рис 6.49а. Оставшиеся входы iRz и Sz выполняют функцию входов / и/С. Анализ работы триггера производится так же, как ранее. Но в данном случае дополняющими являются и выходы главной памяти, поэтому достаточно рассматривать только две внутренние переменные - t/i, yz. Алгебраические выражения функций Yi и Yz занесены в карту на рис. 6.496, в которой обведены кружком все устойчивые состояния. В карте на рис. 6.49в жирной линией показаны изменения состояния триггера при дополняющих сигналах на входах JK- В карте на рис. 6.49г показана функция Т. На обоих входах - / и К - имеется постоянный сигнал 1, и триггер меняет свое состояние после каждого тактового импульса. В карте на рис. 6.49<3 показаны возможные изменения выходов триггера в случае, если во время действия тактового импульса изменяются сигналы J и К. Эти изменения состояния входов приводят всегда к определенным состояниям, однако критическими являются одновременные изменения входных сигналов со значений С=00 и JK=Ol. Возможное влияние этих изменений должно быть учтено при использовании триггера в асинхронных счетчиках. Некоторые варианты схемы. В основной схеме на рис. 6.47а асинхронными входами So и iRd устанавливается в исходное состояние только вспомогательная память. Но при использовании триггера в некоторых схемах это невыгодно. У триггера на рис. 6.50а асинхронными входами Sd ч Rd в требуемое исходное  Рис. 6.50. а) Синхронный iRS-триггер с установкой главной и вспомогательной памяти с помощью входов tRn и S; б) главная память состоит из элементов И/ИЛИ-НЕ состояние устанавливается и вспомогательная, и главная память. Схема, конечно, может быть составлена на любых базовых элементах. Например, во вспомогательной памяти могут быть использованы элементы ИЛИ-НЕ, а в главной памяти -И-НЕ, оба запоминающих устройства могут быть составлены из одинаковых элементов или могут быть использованы комбинированные схемы И/ИЛИ-НЕ и т. п. На рис. 6.506 показана схема, имеющая главную память на элементах И/ИЛИ-НЕ. Синхронные RS-триггеры, управляемые одним фронтом импульса ТИ: Схема несложного триггера показана, на ..рис. 6.51.  в принципе она состоит из трех запоминающих устройств - АВ, CD и EF. При отсутствии тактового импульса, т. е. при ТИ=0, В = 1 и С=1, поэтому изменения состояния входов R к S не могут оказать Q влияния на состояние выхода Q. После изменения состояния входа ТИ со значения ТИ = 0 на значение ТИ=1 выходы В и С перейдут в состояние, соответствующее информации на входах R и S перед Рис. 6JSt. Синхронный RS- появлением тактового импульса. В зави-тригг), управляемый одним симости от того, В = 0 или С = 0, блокв-фроятом тактового импуль- руется работа схем А, С или В, D, а выход Q перейдет в соответствующее состо- ти=о SR ТН=0 ТН = 1- \ i I 00 01 11 w\w II 01 00\00 01 11 I0\l0 11 01 00 010 МО 101 100 Критические послеВобатеттста Th=0 7И=/ r«=o У,УгУз 00 01 и I0\l0 11 01 00\00 01 11 10 10 11 01 00 DID 010 111 101

УгУ2+Уф Ys=Ryj*rHy, ffpomi/i/ecme ПоследоВательтпа Рис. 6.SS. Анализ синхронного JS-трнггера на рис. 6.51: а) карта функций Yi, Yi, Уз для триггера с добавочными инверторами иа входах if, S и карта переходов; б) карта функций Ft, Уа, Уз триггера без добавочных ивверторов на входах R, S и карта переходов яйие. В отличие от всех рассмотренных ранее схем, состояние выхода Q здесь изменится еще во время длительности тактового им- • пульса ТИ=1. Чтобы такие триггеры могли совместно работать, необходимо обеспечить блокирование работы схем А, С или В, D - до того, как изменится состояние выхода Q. Этого можно досшчь, используя схемы с разной задержкой. Работу триггера наглядно показывают функциональные карты на рис. 6.52. Карта на рис. 6.52а справедлива для схем с добавочными инверторами на входах R и S. Обратим внимание иа то, что при 5. = 00 недостаточно блокированы входы SR во время действия тактового импульса ТИ-1. Под действием импульса помех на входе R при Q = 0 после тактового импульса триггер переключится в состояние, соответствующее состоянию входов S=01 вместо правильного SR = 00, и хотя состояние выхода Q не изменится, это все же неправильное состояние. Импульс помех яа входе S неправильно изменит состояние триггера с Q=0 на Q=l. Состояние SR= II недопустимо, так как под действием критических последовательностей триггер может перейти в любое ео- У» ТИ=0 ти=г ти=о ТИ=1 у,У2У\00 01 11 W\W 11 01 00\00 О! П W\W 11 01 00

Критические последовательности. У, = УгТИ+у1Уз-у1ТИ Уг-у,Уз-5уз*5ТИ Уз-Ш + (Уг*КТИ Рис. 6.53. а) Сиихроииый RS-трнгтер с блокированием входов RS во время действии тактового импульса ТИ-1; б) карта функций Yt, У г. Уз и карта переходов [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [ 68 ] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0138 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||