|

|

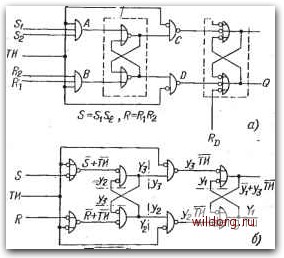

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [ 66 ] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] - вход триггера В и блокируется передача информации со входов R, S триггеру А. Такая же функция может быть обеспечена, если на входные ключи С подаются тактовые импульсы ТИ, а на ключи передачи Z) -их инверсия ТИ (рис. 6.466). При уровне ТИ = 1 входная информация записывается в главное запоминающее устройство, которым является триггер Л, и одновременно блоки- П Л IaOza D В rt>°- тн О Главная пашгш Втмогсшель- налпамть ти ~1ги Рис. 6.46. а) iS-триггер, управляемый сдвинутыми по времени тактовыми импульсами ТИ], ТИг; б) инверсными тактовыми «мпульсами; в) вид тактового импульса ТИ руется передача информации во вспомогательное запоминающее устройство, которое представляет триггер В. При ТИ=0 информация передается из главной памяти во вспомогательную и одновременно блокируется поступление информации в главную память. Для обеспечения надежной работы триггера необходимо во время изменения тактового импульса блокировать главную или вспомогательную память. Входные и передающие ключи С и D должны быть такими, чтобы они реагировали на уровни тактового импульса, показанные на рис. 6.46в: а) в момент ti блокируются ключи D, в результате чего нарушается связь между главной и вспомогательной памятью; б) в момент 4 срабатывают входные ключи С и информация со входов Я, S помещается в главную память; в) в момент 3 блокируются входные ключи С и прерывается передача информации со входов R. S в главную память; г) в момент ti срабатывают передающие ключи D и информация с выхода главной памяти помещается во вспомогательную память. Из представленного описания вытекает, что отдельные запоми-на1ющие устройства управляются различными уровнями тактовых импульсов; с точки зрения общей работы триггер управляется фронтами тактовых импульсов. В качестве запоминающего устройства может быть использован любой • подходящий базовый /PiS-триггер. Так как входная информация передается в главное запоминающее устройство во время действия соответствующего уровня тактового импульса, то импульсы помех этого уровня могут неправильно изменить работу схемы. Поэтому время передачи информации в память, а значит, и длительность тактового импульса должны быть как можно меньше. Однако преимуществом триггеров с главной и вспомогательной памятью является незначительная зависимость их работы от крутизны и характера фронтов тактовых импульсов. В зависимости от требований, предъявляемых к работе, могут существовать как простые, так и очень сложные схемы, но в любом случае они экономичны только в технике интегральных схем. Достижимая частота переключения меньще, чем у триггеров, управляемых одним фронтом тактового импульса. С точки зрения логики такие схемы составляются для функций RS, Т и JK. У триггеров, управляемых одним фронтом тактовых импульсов, информация передается триггеру только во время изменения тактового импульса, причем в положительном или отрицательном направлении в зависимости от схемы включения триггера. У триггеров на дискретных элементах управление одним фронтом может быть обеспечено очень легко с помощью соответствующих входных ключевых схем с емкостными связями. Но этот принцип редко используется в интегральной технике. Главной причиной является не трудность реализации конденсатора в интегральной схеме, как это часто указывается, а сам принцип, который не позволяет достичь максимальных частот переключения при одновременном выполнении других важных требований, предъявляемых к свойствам триггеров. Этот принцип пригоден только для несложных триггеров типов iRS и RS-T. Следующий способ управления одним фронтом заключается в использовании задержек отдельных цепей для блокирования ввода информации в триггер после ее поступления в триггер. Эта функция, конечно, должна быть выполнена раньше, чем полученная информация изменит состояние выходов триггера. Этот принцип может быть рекомендован для триггеров типов JK и D, он основан на использовании трех запоминающих устройств. Основным преимуществом способа управления одним фронтом тактовых импульсов является возможность получения высоких частот переключения, не менее важна также небольшая чувстви-тел.ьность триггера к внешним сигналам помех, которые могут воздействовать на триггер только в течение очень короткого времени действия фронта тактового импульса. Триггеры, в которых используются элементы временной записи информации в форме зарядов, управляются обоими фронтами тактовых импульсов. Синхронные /?5-трштеры Л8-триггеры,\правляемые двумя фронтами тактового импульса. Схемы этих триггеров могут значительно отличаться в зависимости от способа их реализации в базисе цифровых элементов, но их логические схемы и функции, в принципе, одинаковы. Основная схема показана на рис. 6.47а. Главное запоминающее устройство Главная память ± Вспомогательная память i О  Y=ys(ff+TH)=yR,-y7H У-иНИМ-УгГИ . Рис. 6.47. Анализ синхронного -триггера, управляемого двумя фронтами тактового импульса: а) основная схема; б) упрощенная схема для определения функций Ki, Yz, У* состоит из двух элементов ИЛИ-НЕ, управляемых входными ключами А, В. Принцип действия триггера вытекает из символов, использованных в схеме. Входы и выходы без кружков обозначают активные сигналы 1, входы и выходы, отмеченные кружком, обозначают активные сигналы 0. Ясно, что на входные ключи и главную память могут оказывать влияние только сигналы 1, на передающий ключ должны одновременно воздействовать сигнал ТИ=0 и сигнал 1 из главного запоминающего устройства, на [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [ 66 ] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0094 |