|

|

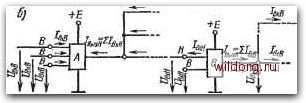

Главная страница Систематические методы минимизации [0] [1] [2] [3] [ 4 ] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] заряда нагрузочных конденсаторов выгодно уменьшать величину коллекторного сопротивления R. Однако ряд факторов ограничивает минимальное значение этого сопротивления и в основных схемах цифровых рядов приходится иметь дело со сравнительно большим временем переключения с уровня Н на уровень В. В схемах на дискретных элементах это время может быть сокращено с помощью цепи ограничения на диоде (рис. 1.7в). Однако в интегральных схемах, имеющих только од«о напряжение питания, значительно более выгодно использовать активный выход. Схема с активным выходом показана на рис. 1.8с. Под активным выходом имеется в виду выход, обеспечивающий ускоренный заряд нагрузочного конденсатора через активный элемент. Роль такого элемента на рис. 1.8а выполняет  а) 1 1 1  Ф 1 11  ; I 1 -fei Ушатт "{чк)У (Тт1 с составным ! "ЗЬр транзистором г; I I  Рис. 1.8. с) Принцип включения с активным выходом; б, в) обеспечение запирания транзистора Гз диодом Д; г) активный выход с составным транзистором транзистор Гз- При уровне В на входе транзистора Ti в насыщенном состоянии будут транзисторы Ti и Гг, а транзистор Гз должен быть заперт. Для обеспечения запирания Гз иа практике используется диод Д, включенный последовательно с эмиттером или с базой транзистора Гз по схемам на рис. 1.86, в. Составной транзистор в схеме рис. 1.8г используется в схемах с очень большим быстродействием. Принцип действия всех схем в основном одинаков. Рассмотрим, например, схему на рис. 1.86. При запирании транзистора Г, а значит, и транзистора Га нагрузочный конденсатор быстро заряжается через небольшое сопротивление Гз и ограничительный резистор R с сопротивлением порядка 100 Ом. Использование активного выхода характерно для быстродействующих схем типа ТТЛ. В интегральных схемах других типов и в схемах на дискретных элементах используются специальные способы построения активного выхода. Кроме рассмотренных схем, предназначенных для различного числа управляющих входов, для расширения возможностей цифровых схем используются триггеры, мультивибраторы, усилители мощности и т. п. 1.3. РАЗВЕТВЛЕНИЕ ВХОДОВ И ВЫХОДОВ ЦИФРОВЫХ СХЕМ На рис. 1.9с представлен пример взаимного включения цифровых схем. К выходу схемы X, имеющей т входов, подключено п схем того же типа. Каждая из этих схем может иметь свое число входов, а к выходу каждой схемы может быть подключено различное число последующих схем. Все эти схемы должны быть составлены таким образом, чтобы они могли работать совместно "г  Рис. 1.9. с) Взаимное соединение цифровых схем; б) рабочие условия с точки зрения разветвления выхода; в) схема с разветвлением входа т и разветвлением выхода п; г) обозначение входа и выхода единичными нагрузками друг с другом и чтобы правила их взаимного включения были как можно проще. При составлении этих правил исходят из основных схем цифровой серии, которые получили наибольшее расаространение. Основной характеристикой данных схем является коэффициент разветвления их входов и выходов. Под коэффициентом разветвления входов понимается число отдельных входов, с помощью которых схема может быть подключена к выходам схем того же, типа. Под разветвлением выходов подразумевается число входов подобных схем, которые могут быть подключены к выходу одной схемы. Обратим внимание на то, что в этих определениях не учитываются величины входных и выходных токов. Рассмотрим, например, схемы двух инверторных элементов на рис. 1.96, использующих принцип подачи тока на выход при уровне Н. Если иа всех трех входах схемы А имеется уровень В, то на каждый вход поступает маленький ток /вх.в, а иа выходе имеется уровень Н. Поэтому на выход поступают большие нагрузочные токи /вх.н от .входов всех подклнэченных схем, и общий нагрузочный ток выхода равен /вых.н=5;/вх.н. Так как на одном из входов схемы В имеется уровень Н, то с его выхода с уровнем В каждая последующая схема потребляет малый ток /by.b<ICbx.h. Ясно, что правила включения значительно упростятся, если как можно большее число элементов будет имет! одинаковые токи /вых.н, /вх.н, /вых.в и /вх.в, определенные при одинаковы» рабочих условиях. В этом случае каждая схема будет характеризоваться коэффициентами разветвления входов т и разветвления выходов п (рис. 1.9е). Надример, для схем ТТЛ типа SiN74 /вы1.н=116 мА, /вх.н = 1,6 мА, вых.в=400 мкА, /вх.в=40 мкА. При выходном уровне Н коэффициент разветвления выхода будет «Н = вык.н/4х.Н = 10/зх.Н Двх.Н = 10. (1 .2) а при выходном уровне В «В = /вых.вДвх.В=10/вх.в вк.В = 10- (1-3) Так как значение коэффициента разветвления в обоих случаях одинаково, тс справедливо, что " = 4ых.Н вх.Н = W.B вх.В = 10 • (1 -4) Токовую нагрузку схемы характеризуют коэффициенты входной нагрузки и нагрузочной способности. Коэффициент входной нагрузки зависит от величины тока, протекающего через один вход при заданных рабочих условиях. У наиболее часто используемых схем коэффициент входной нагрузки выбирается равным единице и представляет собой единичную входную нагрузку (или просто единичную нагрузку). Коэффициент нагрузочной способности определяет число единичных нагрузок, которые могут бьггь подключены к выходу при заданных рабочих условиях. В представленном выше примере в качестве единичной нагрузки можно рассматривать оба тока - /вх.н и /вх.в- Цифра 1 на входах на рис. .1.9г означает в этом случае единичную входную нагрузку, а 10 означает, что к выходу можно подключить 10 единичных нагрузок. В единичных нагрузках выражают величины нагрузок схем соответствующих рядов. Эти так называемые относительные нагрузки выражаются числом, кратным единичной нагрузке. Пример представлен на рис. 1.10. К выходу схемы типа А можно подключить 10 схем типа Л, или 5 -типа В, или 40 схем типа С. Точно так же к

I 1,25 10 OJS n=io 12,5 2gi,2S) 2,5(1,25) 2.5(1,2$ 1,25 1.25 12.5 г,ЩТ\1г,£- 1,25 lj£]-n 1.25 12,5 1 12,5 0,25 П=50 0,2В 2g!,2S) Ш,2£) 0,25 2М1,гв) 0,2Bt-\\ 021 21,25) 0,25 2,SJ,2~\2,S [025 1,25 1 OJS с \1,2В т 12.5 П = 1 Рис. 1.10. Определение входов и выходов с помощью относительных нагрузок схем, управляемых с выхода схемы: а) А; б) В; в) С [0] [1] [2] [3] [ 4 ] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0134 |

||||||||||||||||||||||||||||||||||||||||||||||||