|

|

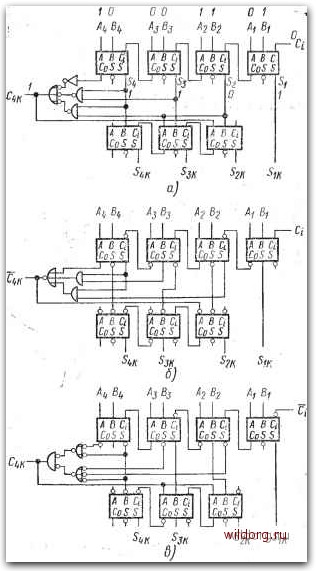

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [ 45 ] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] рис. 5.46 показаны примеры схем с выходом в коде с избытком 3. В корректирующих цепях можно использовать и одноразрядные полные сумматоры. Это решение выгодно при использовании интегральных одноразрядных сумматоров. В схеме на рис. 5.47а использованы сумматоры с одинаковой логической полярностью входа Cj и выхода Со. В схеме на рис 5.476 использованы дуальные сумматоры в такой последовательности, при которой перенос d в сумматор самого младшего разряда активен на уровне В, а перенос С активен на уровне Н.  Рис. 5.47. Примеры схем с «нтегралвными сумматорами: а) с одинаковой логической полярностью Ci и Со; б) с дуальными сумматорами; в) с дуальными сумматорами в обратной последовательности по сравнению с «б> в схеме на рис. 5.47е последовательность сумматоров обратная; Перенос Q в сумматор младшего разряда активен на уровне Ш и перенос активен на уровне В. Оба четырехрзарядных сумматора на рис. 5.476 и в могут работать совместно при сложении десятичных цифр. Очень просты схемы декад, предназначенных для суммирования в коде с избытком 3. На рис. 5.48а имеется схема с однораэ- AjfBfy А3В3 А2В2 А В Ci CqSS IABCi CoSS А BCi CoSS A BCi CdSS A1B1 AifB \ABCi CoSS J-UI [ABC, icoss -.BCi CoSS

A2B2 A BCi CoSS A1B1 A В Сц TT" ABCi CoSS Puc. 5.48. Сложение в. коде с избытком 3: : а) использованы одноразрядные полные сумматоры с одинаковой логической? полярностью переноса Ci и Со; б) использованы дуальные сумматоры fii fij B2 Bi Дополнение ДОООЛ- пение Ai, е« А fij Аг Вг Ai в, Четырехразрядный сштхор -is.- \5ц \5з \sriSt рядными полньши сумматорами с одинаковой логической поляра иостью Ci и Со.У сумматора бит Л* й Вц предполагается наличие выхода с дополняющей функцией Со- На рис. 5.486 - схема, с дуальными сумматорами. Критерием для проведения коррекции служит значение переноса С. Если С4к=0, то сумма на выходах S453S2S] меньше 1111 и корректируется путем вычитания цифры (3) ]о= =(0011)2 [вместо вычитания производится прибавление двоичного дополнения (1101)2],если Ск больше 1, то сумма на выходах 8ц5з828\ больше 1111 и корректируется прибавлением цифры (3) 10= (0011)2- . Принцип вычитания с использованием дополнений показан на рис. 5.49. Если /а = 0 и /в=0, то числа Л и В складываются. Если /а=0, а 1в~\, то создается дополнение числа В, которое прибавляется ж числу л и наоборот. Если вычитаемое число больше, то результат отрицательный и появится на выходах в форме дополнения. Еслк-такой вид результата не годится для дальнейшей обработки, т©> коррекция суммы- Рис. 5.49. Принцип вычитавия с использованием дополнений на выходах Sk-Si могут быть использованы инверторы и вспомогательная цепь, сигнализирующая, что имеет место отрицательное число. Преобразования кодов Полные одноразрядные сумматоры с успехом могут быть использованы для преобразования кодов. На рис. 5.50а показана схема преобразования кода 8421 BCD в код с избытком 3, схема обратного преобразования - на рис. 5.506. Схемы на рис. 5.50в, г. CoSS Коде I избытком D J ВЦ21 .Под с избытком л 3 10 \1 1 I г-] ,I I О Тщ lA вел CoSs\ \CoSS\ Коде избытком I

в A О \ 01 J-Sl JL-L-Ц в А А BCi \CoSS FT Lirrr 81,21 Код с избытком J) I J  Рис. 5.50. Примеры схем преобразования кодов: а) кода 8421 в код с избытком 3; б) кода с избытком 3 в код 8421; в), г) модификация схем «с», «б» выполняющие ту же функцию, комбинируются из сумматоров и базовых элементов ИЛИ-НЕ или И/ИЛИ-НЕ. Также просто могут быть составлены схемы преобразования в код 2421, Грея и др. Полные одноразрядные сумматоры позволяют осуществить параллельное преобразование двоичнозакодированных десятичных чисел в двоичную систему. Схема значительно проще, чем последовательное преобразование со сдвиговыми регистрами, которое будет рассмотрено в соответствующей главе. Принцип прост: любое число, например (85) ю, можно представить в следующем виде: (85)io = 8-10-Ь5.1 = (1000)2-(lO)io-b (0101)2-(l)io = (1000)2-(8+ +2)io-b (0101)2- (l)io== (1000)2-24- (1000)2-24- (0101) -20. Умножение данного числа на 2" означает сдвиг двоичного числа на п позиций влево, т. е. в рассматриваемом примере справедливо (о101)2в=оооо101=5 ; (1000)21=0010000=16 (1000)2=1000000=64 -сумма 1010101 = 85. [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [ 45 ] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0125 |

|||||||||||||||||||||