|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [ 38 ] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128]

00 01

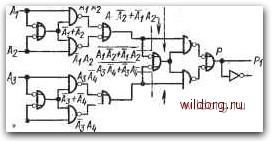

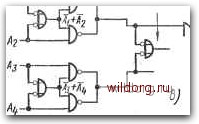

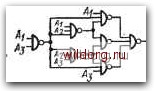

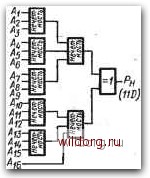

.А1Л2 - AiA2+AfA2. UiA2iAiA2)(AjAfAA)  V,A2+AiAj(A3Ai+AgAj AjAi+AjAu- 6) P=(A1A2+A,J2)(lЗ+/ЗИзh+Щ)(MA2+Щh) {A,A2i-AiA2)(A3A+AsAjJ-  4A,Ai+A,A2](AiA,,+A;sh) Puc. 5.23. Последовательность составления схемы контроля нечетности четырех бит: а) комбинационная таблица и минимизация выходной функции; б) результн-. рующая схема на базе ИСКЛЮЧАЮЩЕЕ ИЛИ; е) упрощение схемы с использованием логики на объединенных выходах а) Pi может быть использован для контроля нечетности четырех бит или в качестве генератора четности четырех бит; б) Рг может быть использован для контроля четности или как генератор нечетности. На рис. 5.23в показана упрощенная схема с использованием логики на объединенных выходах. Преимуществом такой схемы является меньше число уровней логики. Преимуществом схемы на рис. 5.236 является более простая злектромехавическая конструкция при использовании типовых интегральных, схем, потому что каждая схема ИСКЛЮЧАЮЩЕЕ ИЛИ представляет собой основной блок с четырьмя элементами И-НЕ с двумя входами каждый, заключенными в один корпус. Если в схеме рис. 5.236 используются элементы ИЛИ-НЕ, то результирующие выходные функции двойственны выходным функциям схемы в базисе И-НЕ. С точки зрения наглядности будем рассматривать далее только схемы контроля четности. Из базовых элементов на рис. 5.24а могут быть составлены схемы контроля четности в пирамидальном построении. Нагляд- ные примеры контроля нечетности различного числа бит представлены на рис. 5.246. Для контроля нечетности более выгодно использовать базовые элементы И-НЕ, и, наоборот, для контроля четности более выгодны элементы ИЛИ-НЕ. В скобках у выходов Яечетиоспь Задержка лёрёШчП Задержки ЛёректЗЛ А Аз  >Jn= Рис. 5.24. Схема контроля четности: а) основные элементы; б) схемы, предназначенные для различного числа бит указана результирующая задержка распространения сигнала в предположении, что D - задержка- распространения элемента И-НЕ. Принцип пирамидального построения схемы прост. Если .Р„2 - нечетность двух бит - Аи Аг, то справедливо: = =A-iAi-TААг. Для большего числа бит нечетность определяется следующим образом: 3 бита: Рнз=-Рв2+н2Л=(4Ф2)4+0104)Л; И 4 бита: Рш=Р\+Р„Лз=(Л1®А)(А@А)+{А®А){А@А,у, 5 бит: Рн5 = Рнйб+~Рн45 = (\ © 2Г(4©4)Л+Р1фЛ) (з©Л)4-Ь +(А©Л)(/1з®4)Д+(/]1®/12)(/1з®/14)/1б и т. д. С увеличением числа коитролируемых бит пирамида увеличивается и растет также задержка распространения сигнала. Эта задержка может быть уменьшена за счет использования базовых схем, обеспечивающих контроль большего числа бит, чем  , Задержка ) распростпранения 41 1 Задержка распространения 51} -1-Рн i-Рн  Рис. 5.25. а) Базовая схема контроля нечетности трех бит; б) базовая схема! контроля четности трех бит; в) примеры схем контроля нечетности различного-.. числа бит 2. На рис. 5.25с показан пример базовой схемы контроля нечетности трех бит: Аи Аг, Ag. При составлении схемы исходят из ал-: гебраического выражения Pb=AiA2A3+AiA2A3+AiA2A3+AiA2A3. .- Схема контролирует нечетность трех бит при использовани элементов И-НЕ и ИЛИ-НЕ. В схеме в базисе И-НЕ на выходе будет 1 (уровень В) тогда, когда на входах нечетное число единиц (уровни В). В схеме в базисе ИЛИ-НЕ на выходе 1 (уровень В) тогда, когда на входах четное число единиц (уровни В). На рис. 5.256 представлена схема контроля четности трех бит, при составлении которой исходят из алгебраического выражения Ps=As+AiA2As+AiA2A3+AiA2Az. И эта схема выполняет [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [ 38 ] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0116 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||