|

|

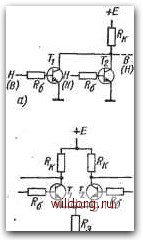

Главная страница Систематические методы минимизации [0] [1] [ 2 ] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] о 1 В) эмиттерный ток /э=0, а через коллектор и базу протекает незначительный обратный ток /„.б.о. Транзистор в этом случае полностью заперт. Во всех остальных схемах на рис. 1.3а через коллектор протекает ток больший, чем /к 6 о- Наихудший вариант с точки зрения запирания представляет случай с отключенной базой при /б = 0, когда величина тока коллектора /н.э.о«р/к б.о зависит от коэффициента усиления тока транзистора. На рис. 1.36 представлена типичная схема, используемая для полного запирания транзистора в схемах на дискретных элементах. В интегральных схемах с одним напряжением питания транзисторы работают в области неполного запирания. В схеме на рис. 1.3в обеспечивается хорошее запирание транзистора Гг, если на выходе насыщенного транзистора 7*1 напряжение составляет 0,1-0,2 В. При большем значении входного напряжения, соответствующем уровню Н, хорошее запирание транзистора обеспечивается кремниевым диодом д (рис. 1.3г). Если на диоде в прямом направлении имеется напряжение 0,7 В, то транзистор надежно заперт и при входном напряжении 1 В. Такую же функцию выполняет переход эмиттер - база транзистора Ti в схеме на рис. 1.3(3. Соединение транзисторов в определенной схеме между собой обеспечивается путем непосредственной связи, связи через пассивные элементы и связи через активные элементы. Такое соединение очень важно, так как оно увеличивает функциональные возможности схемы. В схеме с параллельным включением транзисторов на рис. \Аа уровень В на общем коллекторном выходе будет Рис. 1.4. а) Параллельное включение транзисторов; б) последовательное включение транзисторов; в) эмиттерная связь; г) принцип переключения тока  S) 1  B(rij-

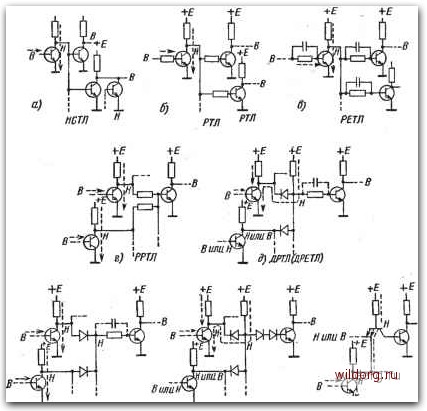

Jf(B) только в том случае, если на входах обоих транзисторов будет уровень Н. В схеме с последовательным включением транзисторов на рис. .1.46, наоборот, на выходе Гг уровень Н имеет место только тогда, когда на входах обоих транзисторов имеется уровень В. Схема с эмиттерной связью на рис. 1.4в является, в принципе, комбинацией схем с общим коллектором и с общей базой. Благодаря наличию общего резистора >Rs оба эмиттера оказывают друг на друга влияние в зависимости от величины управляющих сигналов иа обоих входах. Такая схема, в которой транзисторы могут работать как в насыщенном, так и неиасьш1енном состоянии, находит широкое применение в различных цифровых схемах и прежде всего при создании самых быстродействующих цифровых скем типа ЭСЛ, использующих транзисторы в ненасыщенном состоянии. Принцип включения таких схем показан на рис. 1.4г. В общем - это управляемый током дифференциальный усилитель, который сравнивает уровень сигнала на входе Ti с постоянным уровнем опорного напряжения на входе Tj. Резис- тор J?3 С напряжением - Е представляет собой источник тока, протекающего через Ti или Тц, в зависимости от того, на базе какого из транзисторов более положительное напряжение. Если иа базе транзистора Ti имеется уровень Н, более отрицательный, чем уровень опорного напряжения на базе Тг, то ток протекает через Tz, а транзистор Ti заперт. И наоборот, если на базе Ti имеется уровень В, более положительный, чем уровень опорного напряжения, то ток проходит чез Ti, а транзистор Tj заперт. На рис. 1.5 представлены различные возможные связи между коллектором управляющего транзистора и базой управляемого транзистора. В зависимости от способа связи используются следующие обозначения отдельных схем: -В .  е) дт(др£тл) ж) МЛ 3) ТТЛ Рис. 1.5. Связь между коллектором управляющего транзистора и базой управляемого транзистора в схемах: а) НСТЛ; б) РТЛ; в) РКТЛ; г) РРТЛ; д) ДРТЛ; е) ДРТЛ; ж) ДТЛ; 3) ТТЛ НСТЛ - транзисторные логические схемы с непосредственной связью. Как видно из рис. ,1.5а, элементами этих схем являются транзисторы и коллекторные резисторы. В связи с целым рядом серьезных недостатков эти схемы не используются в качестве основных блоков цифровых систем. Однако сам принцип непосредственной связи используется во многих схемах на дискретных элементах и особенно в интегральных схемах; РХЛ -транзисторная логическая схема с резисгивной связью. Принцип построения схемы представлен на рис. 1.56. Эти схемы находят применение в цепях на дискретных элементах и в интегральных схемах; РЕТЛ - транзисторная логическая схема с резистивной связью и с ускоряющим конденсатором. Схема представлена иа рис. 1.5е, она используется преимущественно с дискретными элементами. Конденсатор, включенный параллельно резистору возбуждения базы, обеспечивает большое переходное перевозбуждение транзистора и значительное сокращение времени переключения. В интегральной технике этот принцип используется для создания схем с очень малой мощностью потерь, так как для получения такого же времени переключения, как в схемах РТЛ, могут быть применены резисторы связи со значительно большим сопротивлением; РРТЛ - транзисторная логическая схема с многократными резистивными связями. Принцип его действия показан на рис. 1.5г. Схема обеспечивает экономичное включение дискретных элементов и смешанных интегральных схем; ДРТЛ-транзисторная логическая схема с диодно-резистивными связями. На рис. 1.55 и е представлены два возможных варианта этой схемы, чаще используется включение, показанное на рис. 1.5<Э. Для сокращения времени переключения параллельно сопротивлению возбуждения базы пожлючаются конденсаторы (ДРЕТЛ) подобно схемам РЕТЛ. Оба варианта используются в схемах иа дискретных элементах; ДТЛ - транзисторная логическая схема с диодными связями, способ построения схемы показан на рис. Л.Ъж, его можно рекомендовать главным образом для интегральных схем; ТТЛ - транзисторная логическая схема с транзисторными связями. Как видно из рис. 1.5з, элементом связи здесь является транзистор с несколькими эмиттерами. Использование такой схемы на дискретных элементах было бы очень дорого, поэтому она находит применение исключительно в интегральных схемах. Реализуемая каждой из этих схем логическая функция выражается зависимостью выходных уровней сигналов от входных подобно тому, как это сделано для рассмотренных выше схем рис. 1.1. Перечень функций отдельных схем с соответствующими обозначениями представлен в табл. 1.1. Основным символом обозначений является сегмент, символ функции ИЛИ отличается от символа функции И тем, что входы заходят внутрь сегмента. Символом уровняН является кружок. Символам, выражающим функции отдельных схем, соответствуют определенные функциональные таблицы, задающие зависимость уровня выхода F от уровней входов X к Y. Рассмотрим, например, функцию пассивной схемы ДЛ (первая строка). Согласно таблице уровней на выходе F будет уровень В только в том случае, если одновременно на обоих входах - X к Y - будет уровень В. Если считать активным уровень В, то функция схемы будет обозначена как символ И без кружка. Из таблицы уровней далее следует, что на выходе F будет уровень Н тогда, когда уровень Н имеется иа входе X, или на входе У, или на обоих одновременно. Считая активным уровень Н, функцию схемы можно обозначить символом ИЛИ с кружками на обоих входах и на выходе. Аналогично можно получить символы всех остальных схем, например, схемы ДТЛ (7-я строка табл. 1.1). Согласно таблице уровней на выходе F будет уровень Н только тогда, когда одновременно на обоих входах - X и Y - имеется уровень В. Считая, что выход достигнет активного уровня Н при активных уровнях В иа входах, получим символ И с кружком на выходе. Кроме того, из таблицы уровней следует, что уровень В на выходе F возможен в том случае, если на входе X, или на входе У, или на обоих одновременно имеется уровень Н. Предполагая, что на входах имеется активный уровень Н, который обеспечит активный уровень В на выходе, функцию схемы можно изобразить символом ИЛИ с кружками на входах. Такой способ интерпретации функций цифровых схем имеет ряд преимуществ с точки зрения наглядного изображения и чтения функций логических схем. Для взаимного соединения схем большое значение имеет способ нагрузив их выходов, в зависимости от которого различают схемы, дающие ток на выход управляющей схемы, и схемы, потребляющие ток с ее выхода. [0] [1] [ 2 ] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0137 |