|

|

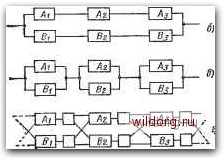

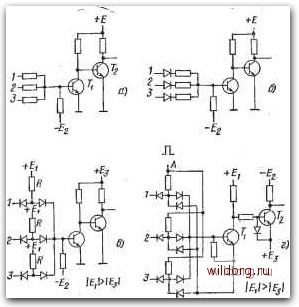

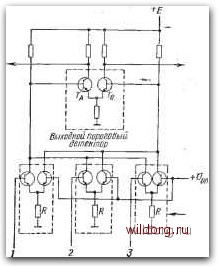

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [ 14 ] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] .Схемы, рассчитанные по методам наихудшего случая, надежно работают в течение всего срока службы в заданных пределах прн отсутствии внезалвого откаЬа. В некоторых случаях к точности используемых элементов предъявляются такие требоваиия, что затрудняется расчет схемы. С этой тсяки зрения более выгодны статистические методы расчета, ио здесь, в отличне от (методов наихудшего .случая, допускается определенная вероятность отказа схемы, который может иметь место раньше, чем отклонение параметров элементов перейдет в область, соответствующую концу срока службы. Число отказов зависит от числа элементов, работающих вне допусков. Статистические ыетоды значительно более трудоемки и требуют большой точности решения. QpaaHH-тельно небольшая ошибка в расчетах, которая в методе наихудшего случая почти не отразится на результате, здесь увеличит вероятность отказа до неприемлемых значений. Поэтому на практике отдается предаточтение методам-наихудшего случая •>. В.незапный отказ схемы проявляется в отчетливом изменении характеристики соответствующего элемента. Причиной могут явиться удар, вибрация, влажность и электрические или тепловые нагрузки. Неисиравяости, вызванные электрическими и тепловыми нагрузками, можно ограничить за счет оптимизации расчета схемы с учетом достижения минимальной мощности потерь. Важно также ограничить временные отказы Ч Их причиной могут быть, например, помехи, воз.никающие в .системе под действием разнообразных связей, времеяибй чрезмерной нагрузки схемы .или ее части, временного изменения, задержки сигнала в частях системы, имеющих критические временные условия, и комбинации различных .случайных факторов. Наиболее важной причиной нарушения .работы системы являются возникающие в ней помехи. Анализ, помех в системе и методов их ограничения представляет самостоятельную сложную проблему, которая будет рассмотрена в соответствующей главе. Также важна и проблема охлаждения системы: механическая конструкция должна бать рассчитана с точки зрения достаточного охлаждения таким образом, чтобы температурный градиент между элемента,ми и окружающей средой был в надежных пределах. Резервирование Значительное увеличение надежности обеспечивает .резервирование технического оснащения системы. Под этим подразумевается добавление резервной, избыточной техники для обработки сигнала. Резервирование может быть использовано на .различных функциональных уровнях - от уровня системы до-, уровня схем и элементов. На рис 1.33а систему представляют три включенных последовательно элемента - А±, Аг, Аз. Ясно, что отказ одного из них вызовет выход из строя всей системы. Рисунок 1.336 демонстрирует резервирование на уровне Ьисте.мы. К основ-нон системе подключена параллельно такая же система, составленная из элементов B,sj4i, Bz=-2 и Вз=Аз, т. е. это дублированная система. В этом случае систама работает нормально при одной или нескольких неисправностях в цепи элементов А или В. Отказ всей системы будет иметь место в том случае, если одновременно появится неисправность в цепочках элементов А и В. На рис. 1.33в представлен пример резервирования на самом низком уровне. В этом случае система работает нормально при одновременных отказах элементов А, В, за исключением одновременных отказов элементов AiBi, АгВг, AsBs. С точки зрения определения места повреждения выгодно так называемое мажоритарное резервирование, принцип которого представлен на рис. 1.34. Важной частью схемы является мажоритарная цепь. .Последняя нредставляет собой Автор имеет в виду расчет схем без использования ЭВМ. При их использовании следует отдавать предпочтение статистическим методам расчета. (Прим. ред.). Для отказов, вызываемых помехами, чаще используется термин «сбой». (Прим. ,ред.}. схему, которая имеет нечетное число (входов, «апример п=3, и выдает сигнал только тогда, когда имеется сигнал одновременно на (п+1)/2 и больше ходах. На рис. 1.34а приведен пример резервирования на самом низком уровне с мажоритарным принципом два из трех. Вместо одной основной схемы В используются три тождественные схемы - Bi, В, Вз, выходы которых подключены ко входам мажоритарной цепи. На выходе мажоритарной цепи правиль- • . , I \-иидикашл Ч-г нтпраЬиоста. 11  ---ffj- -gjln Ошвная схема без резервирований  резервная схема. Выход Основные маокоритарпай схемы цет Е-/ 11-TJ гл мажоритарная L- ео Во/ч принципе - мажоритарная цепь Ф В) Рис. 1.33. а) Последовательное включение трех элементов; б) резервирование на уровне системы; е), г) резервирование на более низких уровнях Рис. 1.34. а) Мажоритарный принцип «два из трех»; б) аналоговый принцип мажоритарной цепи; е) цифровой принцип мажоритарной цепи ный сигнал будт только тогда, когда будут иметь место правильные сигналы на выходах всех трех схем или произвольной комбинации двух из них - В1В2, В2В3, В1В3. Значит, в принципе, мажоритарная цепь исправляет одну ошибку, возникшую в связи с неисправностью одной схемы. Для локализации неисправности можно использовать несоответствие выходов всех трех схем -Bi, В2, В3. Исправление двух одновременных ошибок обеспечивает более высокий уровень резервирования с мажоритарным принципом три из пяти. В этом случае используются пять тождественных основных схем и мажоритарная цель с пятью входами. Мажоритарное резервирование выгодно и на более высоких функциональных уровнях сложных схем, подсистем и т. п. Мажоритарная цепь может быть, в принципе, составлена двумя способами. На рис. 1.346 схематически представлен аналоговый принцип, который заключается в том, что с ростом числа входных сигналов увеличивается напряжение на выходе суммирующей цепи 2. Если число входных сигналов равно или больше чем (п+1)/2, то выходное напряжение суммирующей цепи превысит пороговое напряжение подключенного к ней усилителя, благодаря чему из.менится его выходной уровень. Используя второй способ (рис. 1.34е), можно составить мажоритарную цепь на обычных цифровых схемах. На рис. 1.35а имеется cxeia простой мажоритарной цепи, использующей аналоговый принцип. Если уровень В имеется на всех трех входах или на двух любых входах, то уровень В будет и на выходе цели. Если уровень В - только яа одном входе, то на выходе цепи будет уровень Н. Диоды на рис. 1.356 48 улучшают взаимную развязку входов и уменьшают требования, предъявляемые к допустимым отклонениям элементов. Эти схемы могут быть использованы только вместе с целями, диапазон сигналов которых сравнительно велик. Рис. 1.35. Мажоритарные цепи: а) аналоговая с резистивными входами; б) с улучшенной взаимной изоляцией входов; е) с диодными входными связями; г) пример схемы обнаружения неисправности  На рис. 1.35е представлена схема мажоритарной цепи с диодными входными связями, предназначенная для небольших перепадов сигнала. Единичные входные токи очень хорошо определяются при достаточно больших значениях сопротивлений резисторов R и напряжения £1. Принцип действия такой же, как схемы на рис. 1.35а. На рис. 1.35г приведен пример схемы, предназначенной для обнаружения неисправности. Если на всех входах имеется уровень В или Н, то транзистор Ti заперт, и на выходе схемы будет уровень В. При положительном импульсе на входе А состояние выхода не изменится. Однако если уровни на входах /, 2, 3 неодинаковы, то при положительном импульсе на входе А транзистор Tl откроется и на выходе появится отрицательный импульс, который сигнализирует неисправность. Схема мажоритарной цепи с эмиттерными связями (рис. 1.36) допускает большие отклонения входного уровня В. Напряжение каждого входа сравнивается с постоянным опорным напряжением Пош. Если напряжение на всех трех или двух входах превышает Uon, то соответствующие транзисторы открываются, через эмиттерные резисторы Л про-  ВшоВиые порозоВыв детекторы Рис. 1.36. Мажоритарная цепь с эмиттерными связями [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [ 14 ] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0131 |