|

|

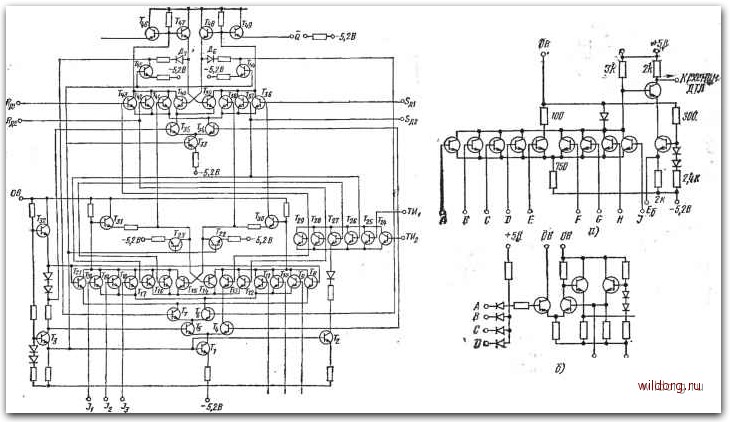

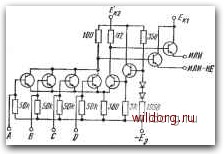

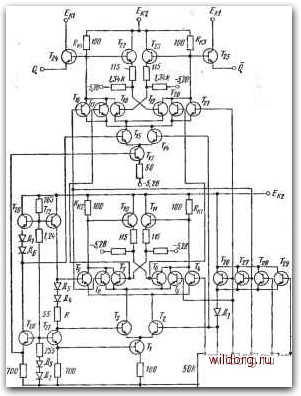

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [ 124 ] [125] [126] [127] [128] -Вро-С=И> Оо.  .о К схемам 6 о •! А/ 2 % Рыс. 7.53. С-триггер с главной и вспомогательной памятью Рис. 7.94. Схемы согласования: а) преобразование уровней сигналов ЭСЛ в уровни сигналов ДТЛ; б) обратное преобразование уровней сигналов ются согласующие схемы. На рис. 7.94с показана схема преобразования уровня сигналов схем ЭСЛ в уровень сигналов схем ДТЛ. Если вход / подсоеди-нить к клемме опорного напряжения Ее, то схема имеет функцию Fi=A+B + +C+D+H. Бели же к клемме £6 подклюяить вход Е, то получим функцию Fi=F+G+H+J. На рис. 7.946 имеется схема преобразования уровней сигналов схем ДТЛ в уровни сигналов схем ЭСЛ. Схема представляет функцию ИЛИ. Интегральные цифровые схемы ряда ЭСЛШ Базовые схемы этого ряда характеризуются очень малыми задержками распространения, порядка 1 не, у триггеров частота переключения - 300- 500 МГц. Достижение таких значений обеспечено, в первую очередь, улучшением производственных процессов, которое позволяет уменьшить геометрию интегральных транзисторов, имеющих граничную частоту 2 ГГц. Схема иа рис. 7.95 в принципе такая же, как представленные ранее схемы ЭСЛ, и отличается прежде всего мощностью ,и параметрами элементов, которые оптимизированы с точки зрения взаимного соединения схем линиями передачи, имеющими характеристическое сопротивление 50 Ом. Коллекторы выходных эмиттерных повторителей подключены к отдельной клемме £„i, благодаря чему эмиттерные повторители отделяются от входных цепей и от источника опорного напряжения, на которые, в свою очередь, не оказывают влияния переходные выходные токи, возникающие из-за неравномерной нагрузки выхода. При переключении выходных транзисторов в течение 1 ис амплитуда переходных токов может достигать 20 мА. На практике клеммы и £«2 подключаются к отдельным проводящим плоскостям заземления многослойных монтажных плат. Выходы могут работать на нагрузку 50 Ом или «а нагрузку 510 Ом. В первом случае ток нагрузки - 22 мА и задержка -1,1 не, во втором случае обе .величины уменьшатся до 8,5 мА и 0,9 не. Так как выходные токи сравнительно велики, то эмиттерные резисторы выходных повторителей отсутствуют. Достоинством такого схемного решения является возможность соединить выходы большого числа схем и уменьшить мощность потерь до 55 мВт. При нагрузке 510 Ом мощность потерь возрастает до 100 мВт. Между базой входных транзисторов и источником напряжения - £э включены резисторы с сопротивлением 50 кОм, которые представляют большое сопротивление для линий передач с последовательным окончанием. Через эти резисторы протекают обратные токи без подключенных транзисторов. Поэтому неиспользуемые входы можно оставить невключенными. В другом варианте этой схемы использованы резисторы с сопротивлением 2 кОм, представляющие нагрузку выхода предыдущей схемы. Эти .схемы могут быть использованы только при очень коротких соединениях между входами и выхода.ми отдельных .схем, когда их не нужно рассматривать как линии передачи. Рекомендуется, чтобы расстояние между (Центрами KOipnycoB схем ие превышало 16 мм. Допустимый уровень .статических помех в диапазоне тем.ператур -55-+.125°С составляет 0,24 В, но температуры отдельных схем не должны слишком отличаться. На рис. 7.96 имеется схема £>-тр.нггера, работающего на принципе главной и вспомогательной .памяти. Допустим, что уровень Н - на входах ТИ, R, S, D и на выходе Q, иа выходе Q - уровень В. В главной памяти ток течет через Ts, Тд, а в вспомогательной - через Тц и Tis- При уровне В на входе D ток переключается с Те яа Tt,, на базе ,и эмиттере Ти в главной памяти - уровень Н, на базе и эмиттере Тю - уровень В и такой же уровень на базе Те- Но несмотря на это, через данный транзистор не может протекать ток, потому  Рис. 7.95. Схема ряда ЭСЛШ что Тг заяерт. Предположим теперь, что на одном из входов ТИ имеет место положительное изменение напряжения с уровня Н на В. Во время положительного изменения этого напряжения ток, протекавший через Тз, потечет в Tz, и так как иа базе Те - уровень В, то через этот транзистор потечет ток. Уровни напряжений «а базах и эмиттерах Тю и Тц не меняются, поэтому уровень В будет и на базе Tjo. Во время положительного изменения ТИ ток с Тц пере-  тшк\ ж оик ж -5,1 в in °Щ Рис. 7.96. JD-триггер с главной и вспомогательной памятью ключится на Тц,, а значит, потечет ток и через Тго. На базе, иа эмиттере Тгз и на базе Tie reneipb уровень Н. Во время отрицательного изменения ТИ с уровня В на Н ток, протекавший через Тц, потечет в Т15 и передача информации между главной и вспомогательной памятью прекращается. Одновременно ток, протекавший через Тг, потечет через транзистор Тз и перестанет течь ток через Ti. Резистор J?=55 Ом обеспечивает разную величину пороговых напряжений главной и вспомогательной памяти. Функциональные возможности ряда ЭСЛП1 расширяют схемы с разнообразными логическими функциями. Возбуждение длинных линий на схемах ЭСЛ На ,рис. 7.97а две схемы ЭСЛ соединены одним проводником, расположенным на большом расстоянии от проводящей структуры заземления. В конце провода, в точке В, возникают затухающие колебания, начальная амплитуда [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [ 124 ] [125] [126] [127] [128] 0.0085 |