|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [ 123 ] [124] [125] [126] [127] [128] swieUioc +75e) swmH-ss°c -rmc)  swwt5(oc +n°c)- swt2l5(-s5c +m°c)  Puc. 7.8. J) iJS-триггер, управляемый более положительным уровнем тактового импульса; б) более отрицательным уровнем тактового импульса sWidie(Dci-m-c)  .swmcoc-+tso) swiz33(-ss%+r2b°c)

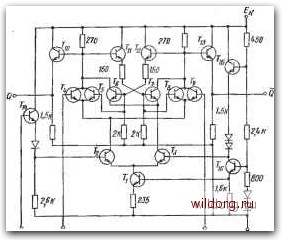

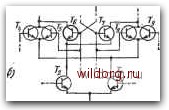

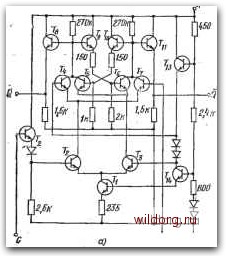

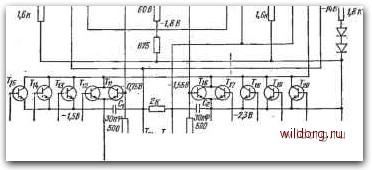

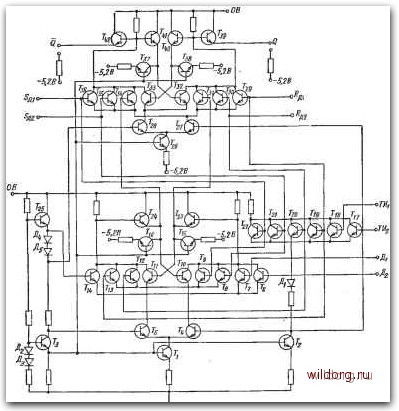

Рис. 7.90. а) D-триггер, управляемый более положительным уровнем тактового импульса; б) более отрицательным уровнем тактового импульса На рис. 7.90а представлена схема D-триггера. Из имеющейся таблицы вытекает, что вход D активен только тогда, когда на входе С - более положительный уровень В. Триггер может управляться более положительными уровнями импульсов на входе D при уровне В на входе С или более положительными уровнями тактовых импульсов на входе С в зависимости от состояния входа D. Триггер, схема которого приведена на рис. 7.906, имеет активный вход D только при более отрицательном уровне Н на входе С. На рис. 7.91 показана схема (-триггера с емкостной связью. Типичная частота переключения - 85-120 МГц, минима.п[ьная гарантированная частота - 70 МГц. Память реализована на транзисторах Ti, Тг и Tg, Т?. Входы Rd и Sj,, S\y l01J(0°C-i- + 7DC) SW 1213(-55% ~ + IZSC) Ia-  -c/P„ llf. .afl 2ir П i5ir \\-ih\ -X V T V 6 4 6 6 Puc. 7.91. С-триггер с емкостной связью используемые для установки требуемого исходного состояния, активны при уровне В. Для большей наглядности в схеме приведены величины постоянных напряжений в случае, если триггер находится в состоянии Q=B, Q = H. В таких условиях напряжения на входах / могут изменяться, не оказывая влияния на состояние триггера. При положительном изменении напряжения на одном из входов К с уровня Н на В напряжение на соединенных эмиттерах Tj-То изменяется со значения -2,3 В на -1,5 В. Этот перепад напряжения через конденсатор Cj передается на Tg, который изменяет состояние триггера. Ток, протекающий через Тгь потечет в Т22, благодаря чему быстро зарядится конденсатор Ci и на триггер опять может влиять положительное изменение напряжения теперь на одном из входов /. При асинхронном режиме работы триггер реагирует только на положительное .изменение напряжения на входах / и К. Однако положительным изменением напряжения на любом входе / триггер может быть установлен в состояние (2=В, Q=H только тогда, когда на всех остальных входах / - уровень Н. Если же хотя бы на одном входе / - уровень В, то положительное изменение напряжения на другом входе / не влияет на состояние триггера. То же самое можно сказать о входах К. Триггер переключается после каждого положитель- иого изменения напряжения, которое появляется одновременно на входе / и входе К. При синхронной работе тактовые импульсы подаются на любые два соединенных входа - /, К- Во время действия уровня В на входе Rd или Sd на входах /, К не должно происходить положительного изменения напряжения, так как на выходах триггера могут возникать сигналы помех, влияющие на работу другого триггера. На рис. 7.92 приведена схема /)-триггера, работающего на принципе главной и вспомогательной памяти. Главную память представляют Гю, Тгз и Гц, Tzi, вспомогательную же - Гзз, Г41 и. Т, Т40. Информация входов D записывается в  -S,2B Рис. 7.92. £>-триггер с главной и вспомогательной памятью главную память во время наличия уровня В тактового импульса на одном из входов THi, ТИ2 и передается во вспомогательную память во время отрицательного изменения тактового импульса. Входы Rd и Sd, которыми триггер устанавливается в исходное состояние, активны при уровне В. Соединяя выход Q с одним из входов, D, или Di, получаем Т-триггер.. Максимальная частота переключения - 200 МГц. На рис. 7.93 представлена схема /ТС-триггера. Она почти такая же, как предыдущая схема, кроме третьего каскада на транзисторах Те и Г?, управляемых с выходов триггера. Максимальная частота переключения также 200 МГц. Для обеспечения совместной работы схем ЭСЛ со схемами, в которых транзисторы работают в насьцценном состоянии (например, ТТЛ, ДТЛ), использу- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [ 123 ] [124] [125] [126] [127] [128] 0.0105 |