|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [ 122 ] [123] [124] [125] [126] [127] [128] пользованы в качестве второго входа Гг или управляющего входа для блокирования входа Гг, г) соединенные входы Ji и Ki используются как вход тактовых импульсов, а оставшиеся входы - /г и Кг - как самостоятельные управляющие входы J и К-В этом случае схема выполняет функцию синхронного Ж-триггера. При уровне SW302lSW352A

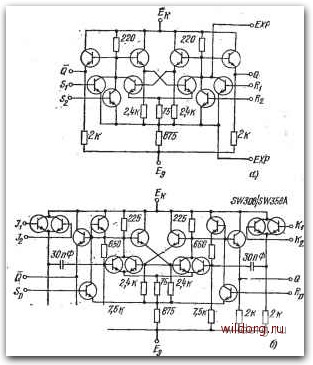

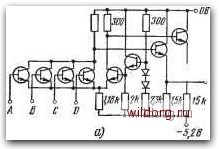

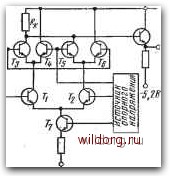

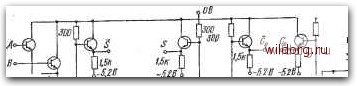

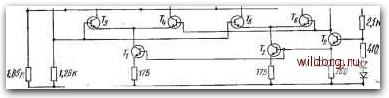

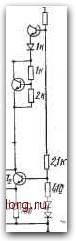

Рис. 7.85. Триггер: а) JRS; б) JK Н тактового импульса пачожительное изменение напряжения на входах J и К может изменить состояние триггера, как бьшо отмечено в п. «а». Прямые входы Ro и Sd, используемые для установки исходного состояния триггера, активны при уровне В, причем без учета состояния входов /, К. На обоих входах-lRu и Su - не должен быть одновременно уровень В. Интегральные цифровые схемы ряда ЭСЛП Этот ряд обладает примерно такими же свойствами, как ряд ЭСЛ1, однако характеризуется значительно большим количеством схем со сложными функциями. Каждая схема имеет свой интегральный источник опорного напряжения, и, в отличие от ряда ЭСЛ1, в корпусе может быть размещено несколько интегральных схем. Базовая схема представлена на рис. 7.86а. Другие схемы отличаются числом входов, отсутствием одного или обоих выходных эмиттерных резисторов, исключением выхода ИЛИ или, наоборот, наличием большего числа выходов ИЛИ и ИЛИ-НЕ, а также возможностью увеличения коэффициента объединения по входу с помощью расширителя. На рис. 7.866 представлена возможность полу- sviwolsvjmif  -A ±B -A->B*C*B -A*B C*B - AjJ+CB -AB-C-B -C*B Puc. 7.86. a) Основная схема ряда ЭСЛП; б) получение добавочных логических функций путем соединения выходов двух схем, каждая из которых имеет три выхода ИЛИ-НЕ и три выхода ИЛИ SWIBJO А о- В о-  <ВЬ АВ*АВ чения различных логических функций с помощью двух схем, каждая из которых имеет три выхода ИЛИ и три выхода ИЛИ-НЕ. На рис. 7.87 показана схема с двухкаскадной логикой функции ИСКЛЮЧАЮЩЕЕ ИЛИ. На выходе схемы будет уровень В, если ток течет через Ti и Ti (при Л = Н, В = В) или через Га и Те (яри А = В, В = Н). При других комбинациях уровней на входах А, В ток течет через резистор Як и на выходе будет уровень Н. На рис. 7.88 приведена схема полного сумматора. Для реализации логических функций сложения и переноса использованы трехкаскадное последовательное включеиие основных двухвходо-вых схем и соединение коллекторов. Задержка функции переноса с входа Ct на выход Со очень мала, около 3,5 не, так как на самсм высоком уровне логики использованы дополняющие переменные Cj, Ci, а яа самых низких уровнях логики переменные А, В сравниваются с постоянным спорным напряжением. Для наглядности на рис. 7.78 приведены значения напряжения, соответствующие отдельным каскадам. Внутренний .источник напряжения рассчитан так, чтобы каждое опорное напряжецие примерно соответствовало середине перепада сигнала независимо от изменения температуры, от колебаний напряжения питания •-5,2 В и от соотношения сопротивлений резисторов. Для разветвленной логической схемы используется всегда только один источник постоянного тока, что обеспечивает .че-иасыщеиное состояние транзисторов первого каскада, постоянные перепады сигналов при изменении уровня на входе В и исключает необходимость в цепи ограничения на выходах соединенных коллекторов. На том же принципе работает интегральный вьиитатель, схема которого отличаетси только тем, что соединены базы Гз, Те и базы Г4, Г5. Выходы разности D аналогичны выходам суммы S, а перенос С,-, Со аналогичен заему Bt, Во. Схемы интегральных триггеров значительно сложнее, чем в ряду ЭСЛ1. На рис. 7.89а; представлена схема /?5-триггера, управляемого более положительным уровнем тактового импульса. Память представляют Г5, Гц и Ге, Г12. При более отрицательном уровне на входе ТИ Г14 заперт, и «и уровни на входах S, Рис. 7.87. Пример двухуровневой логической схемы, реализующей функцию ИСКЛЮЧАЮЩЕЕ ИЛИ sWiSia/sWiiB MCWIS/MCIZW Ps=110 \30d Wjoo   S=ABCitABDi*AeCitABCi  a) -Si§ "6 \300 -0,75B(B) .1,55B(H) ie-B)-2,S25B (AB)-2.Z5B (АН)-гш -зогвв -5,гв Рис. 7.88. а) Полный сумматор; б) напряжения отдельных каскадов ии их изменения не влияют на состояние выходов триггера. В принципе, возможны два способа работы: 1. Управление тактовыми импульсами. При S=B и R=Y\ триггер устанавливается в состояние Q=B, Q = H более положительным уровнем ТИ. Аналогично при S=H, J?=B будет состояние Q = H, Q = B; при S=J?=H состояние триггера не меняется, а при 8=К=Ъ - результирующее состояние триггера зависит от сдвигов сигналов во времени. 2. На входе ТИ имеется постоянный более положительный уровень, а на входах J? и S - обычно более отрицательный уровень. В этом случае триггер работает как простой асинхронный триггер, управляемый более положительными уровнями импульсов на входах R а S. Входы R v. S блокируются более отрицательным уровнем на входе ТИ. Триггер, составленный по схеме на рис. 7.896, имеет входы R v S, активные при более отрицательном напряжении на входе ТИ. Типичная задержка распространения со входа S на выход Q составляет 4-5 не, с входа ТИ на выход Q - 6 НС, т. е. способ управления «2» - более быстродействующий. [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [ 122 ] [123] [124] [125] [126] [127] [128] 0.0093 |

|||||||||||||||||||||||||||||||||||||||||||||||