|

|

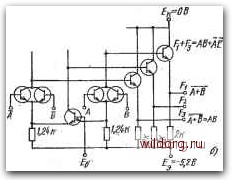

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [ 121 ] [122] [123] [124] [125] [126] [127] [128] Из представленного краткого обзора вытекает, что схемы ЭСЛ имеют много достоинств. Для большей наглядности свойства схем ЭСЛ объединены: . 1. Основным свойством схем ЭСЛ является их большое быстродействие. В этих схемах транзисторы работают в ненасыщенном состоянии, что исключает задержку, овязанную с избыточным зарядом транзистора. Эта задержка является главным фактором, сдерживающим увеличение быстродействия. Достижению высоких скоростей переключения способствуют также небольшие перепады сигналов и малое выходное сопротивление схемы. В схемах серий ЭСЛ1 и ЭСЛП типичная величина задержки распространения составляет <зд.р.ср=4-;-5 не и примерно таково же время включения и выклюнетия - Задержка зд.р.ор, возникающая во время выключения зависит от емкости нагрузочных конденсаторов и скорости их разряда через выходной эмиттерный резистор. При разветвлении выхода п=3 время °зд.р=4н-6 не и увеличивается на 0,66 не на каждую дополнительную единичную нагрузку, подключаемую к выходу. Задержка зд.р, возникающая во время включения t>•, зависит от емкостной нагрузки сравнительно мало, так как нагрузочный конденсатор может довольно быстро заряжаться через транзистор выходного эмиттерного повторителя. Однако при большом разветвлении п и при использовании длинных соединений могут иметь место колебания, связанные с распределенными емкостями и ин-дуктивностями. Задержка распространения зд.р.ср сравнительно мало зависит от изменения напряжения питания; при изменении же температуры от -55 до +1125°С величина задержки возрастает почти на 1007о. 2. Для питания схемы достаточно одного источника напряжения - 5,2 В со сравнительно большим допустимым разбросом ±207о. Источники опорного напряжения интегрированы вместе с основной схемой, они улучшают допустимые уровни помех, но одновременно увеличивают потребляемую мощность и мощность потерь. 3. Постоянное потребление тока от источника питания. В связи с характером включения схем ЭСЛ величины токов, соответствующие отдельным состояниям, отличаются очень мало. В схемах с дополняющими выходами величины этих токов отличаются примерно на 5%, в схемах с одним выходом - менее чем на 2%. Поэтому при использовании схем ЭСЛ почти исключаются проблемы, связанные с возникновением помех на проводах заземления и питания. 4. Малое выходное сопротивление ограничивает возникновение помех па соединительных проводах, связанных с емкостными наводками, а малые выходные токи, порядка 0,1 мА, ограничивают возникновение индуктивных наводок. Малое выходное сопротивление уменьшает также влияние нагрузки на выходной уровень. 5. Малое выходное и большое входное сопротивления позволяют иметь большое разветвление выхода и входа без значительного ухудшения свойств схемы. Максимально допустимое разветвление выхода п=25, однако практически оно зависит от электромеханической конструкции, используемой при монтаже схемы, и от требований, предъявляемых к быстродействию схемы. Паразитные емкости и индуктивности соединительных линий при большом быстродействии ограничивают разветвление выхода обычно до п=15. Коэффициент объединения по входу при большом быстродействии ограничен величиной т=20. У базовых схем максимальный коэффициент объединения по входу т=5. Увеличить т позволяют входные расширители. Если не требуется большого быстродействия, то допускается im>20. 6. Перепад сигналов в схемах ЭСЛ примерно равен напряжению Uco, и типичная величина статических помех составляет 0,24 В. Допустимый уровень помех зависит не только от температуры ИС, но и от разницы температур отдельных ИС. Напряжение (7б.э является основным температурозависимым параметром схем ЭСЛ. Так как транзисторы базовой схемы интегрированы в одной кремниевой пластинке, то температурные различия отдельных напряжений <7б.» пренебрежительно малы, изменения напряжения Uc э при изменении температуры автоматически компенсируются и допустимый уровень помех в рабочем диапазоне температур постоянен. Почти не изменяется также производственный разброс напряжения Us.a- 7. Основные схемы ЭСЛ имеют дополняющие выходы, на которых одновре- . менно имеются функции ИЛИ и ИЛИ-НЕ. Их использование позволяет снизить количество схем на 30%, а кроме того, уменьшается также общая задержка логического функционального блока. 8. Сложные функции могут быть реализованы прямым соединением выходов нескольких базовых схем. Это также экономит схемы и уменьшает задержку. С точки зрения помех, вызываемых наводками, эти соединенные схемы должны размещаться на одной функциональной плате. 9 Каскадирование базовых схем позволяет реализовать сложные интегральные схемы с минимальной потребляемой мощностью и мощностью потерь. Интегральные цифровые схемы ряда ЭСЛ1 ЦИС этого ряда выпускаются для стандартного диапазона температур 0-г--1-75С и для расширенного диапазона - 55-=-125" С. Типичным представителем ряда ЭСЛ1 являются, например, серия SW300/350 (Stewart-Warner), серия МС300/МС350 и серия FNH100 (Telefunken). Ряд отличается сратнительно небольшим числом базовых схем и отдельными источниками опорного напряжения. Напряжение питания - 5,2 В±207о, потребляемая мощность - 35-40 мВт, задержка - 5-7 не. Базовая схема на рис. 7.82а имеет пять входов. Источник опорного напряжения Ев на рис. 7.826 может питать 12-25 базовых схем. У схемы с тремя ) Q Ь Расширитель BxdSde о ил и -оИЛИ-НЕ 2,55к Eg Ef-S,2B r , Lob -оИЛИ -оИЛИ-ОЕ 4J Eff E,--5,ZB Puc. 7.82. Схемы ряда ЭСЛ I: a) базовая схема; 6) источник опорного напряжения; в) возможность увеличения числа входов расширителями входами на рис. 7.82е число входов может быть увеличено с помощью расширителей. На рис. 7.83а приведена несколько измененная основная схема с двумя выходами ИЛИ-НЕ. В одном из вариантов схемы в качестве выхода использован непосредственно эмиттер выходного транзистора без эмиттерного резистора. Схема на рис. 7.836 может быть использована для реализации функции ИСКЛЮЧАЮЩЕЕ ИЛИ, сравнения, неполного сумматора и т. п. Лга? h ISO 290 hgD -aC+D  (A*ei(Md)mA Puc. r.c3. a) Схема с двумя выходами ИЛИ-НЕ; б) схема более сложных логических функций h2ffO . . . !. i-.PB\ -0q2  Pmc. 7.S4. o) Т?5-триггер, составленный из двух схем ИЛИ-НЕ (пунктир - преобразование схемы в ждущий мультивибратор); б) схема Шмитта На рис. 7.84а представлена схема простого Т?5-триггера, составленного из двух базовых схем - ИЛИ-НЕ. Пунктиром показано изменение схемы для получения схемы ждущего мультивибратора, управляемого входом S. На рис. 7.846 показано простое преобразование базовой схемы ЭСЛ в схему Шмитта. Оно заключается в подключении резистора R с выхода ИЛИ-НЕ на базу транзистора, на которую подается опорное напряжение. На рис. 7.85а показана схема асинхронного i/S-триггера. Число управляющих входов R можно увеличить подключением расширителя. На рис. 7.856 представлен интегральный /iC-триггер, реагирующий на положительное изменение напряжения на управляющих входах. Триггер имеет следующие функциональные возможности: а) при положительном изменении напряжения на входе / триггер устанавливается в состояние Q = B, Q = H. Если триггер в этом состоянии, то положительное изменение напряжения на входе / не оказывает влияния на состояние схемы. При положительном изменении напряжения на входе К триггер устанавливается в состояние Q = H, Q = B. Положительное изменение на входе К не оказывает влияния, если триггер уже находится в этом состоянии; б) если на одном входе / - уровень В, то положительное изменение напряжения на другом входе не влияет на состояние триггера. То же справедливо и для входов К; в) если соединить, например, входы Ji и К\, то возникает вход типа Г]. Триггер опрокидывается при каждом положительном изменении напряжегия на входе Ti. Остальные два входа -/2 и К2 - могут быть также соединены и ис- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [ 121 ] [122] [123] [124] [125] [126] [127] [128] 0.0177 |