|

|

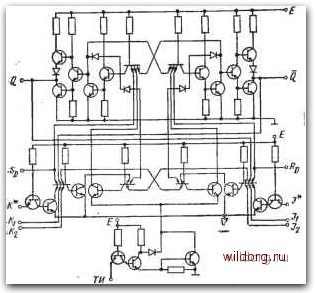

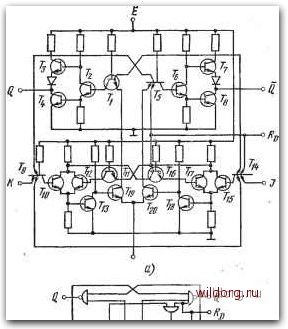

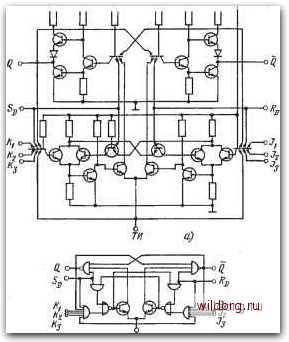

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [ 115 ] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] дизъюнкция. Так как схема имеет большое число управляющих входов J и К, то у триггера только один прямой вход iRd, с которого он устанавливается в -состояние Q=H, Q=B. На рис. 7.59а представлена более сложная схема У/С-триггера, который ре-.агирует на положительное изменение тактового импульса на входе ТИ. И хотя яа первый взгляд схема кажется запутанной, принцип действия ее очень прост. .Для наглядности пунктиром обозначены контуры, соответствующие логической схеме триггера на рис. 7.596. Надежную работу триггера обеспечивают несколько обратных связей. Ос-шовные свойства работы с двумя устойчивыми состояниями обеспечивают обратные связи с выхода А иа эмиттер Ti и с выхода В на эмиттер Т. Обратные •связи с прямых асинхронных входов Rd и Sd на транзисторы Тп и Тг обеспечивают неизменность состояния выходов С и D при установке триггера в нужное исходное состояние. Для входов J а К важны обратные связи с выходов А и б на Т20 и Tib- Допустим, что Q=H, Q = B, /=/,/2/*з=Н, K=KiK2K*ib, Ш=Н. В та-асих условиях заперты Тп и Т21. Если теперь напряжение на входе / изменится -с уровня Н на В, то Тп закроется, Г9 откроется и закроется Тге- В результате запирается эмиттер Т20, и если бы не было обратной связи с выхода А на другой эмиттер Гго, то транзистор Т21 открылся бы и остался в этом состоянии и после изменения напряжения на входе / с уровня В на Н. После окончания тактового импульса состояние триггера изменилось бы, при правильной ра-•боте триггера оно должно оставаться без изменения. Благодаря обратной связи с выходов Q и Q на транзисторах Тп и Т23. состоя-шие выходов С и D не изменяется под действием тактовых импульсов. Допустим, что Q=B, Q=H, /=/i/2/*3=/Ci/C2/C*3=B, на выходе С - уровень В, на выходе D - уровень Н и прервана связь 7"27. Ггв с транзисторами Тп, Т22. Как только тактовый импульс достигнет уровня В, откроется 7"28- Теперь через под-жлюченный эмиттер Тд потечет ток и напряжение на выходах триггера изменит-•ся, стремясь к уровням Q=H, Q=B. Однако это вызовет изменение напряжения ша выходах С и Д откроется Т„, потечет ток через подключенный эмиттер Г,, «опять начнут изменяться состояния выходов триггера и т. д. Без обратных свя-  Рис. 7.60. /7С-триггер, реагирующий на положительное изменение тактового импульса зей триггер бы осциллировал в течение длительности ТИ. Установка триггера с асинхронных входов До и So возможна только в том случае, когда отсутствует тактовый импульс на входе ТИ. По схеме на рис. 7.59 работает, например, триггер типа S8825J. Минимальная длительность тактового импульса - 33 не при минимальной амплитуде 2,6 В. й максимальной длительности фронта и спада 150 не. Мощность потерь - 70 мВт. На том же принципе работает триггер SN7470/SN5470, схема которого представлена на рис. 7.60. Типичная частота тактовых импульсов этого триггера - 35 МГц. На рис. 7.61 показана простая схема триггера с главной и вспомогательной памятью. Главную память составляют Tj-Tg, вспомогательную память с входными цепями - -Tib, и в качестве элементов связи между главной к  Рис. 7.61. а) С-триггер с главной и вспомогательной памятью; б) логическая схема вспомогате 1ьной памятью использованы транзисторы Tig и Тго- Схема имеет только один прямой асинхронный вход Rd. которым устанавливаются состояния Q=H, Q"=B, причем независимо от входа ТИ. По схеме на рис. 7.61 работает,, например, триггер типа SN7473. Его мощность потерь - 40 мВт, /зд.р.ср = 30 не, минимальная длительность ТИ равна 20 не. В одном корпусе размещены два интегральных триггера. На том же принципе работает триггер SN7472, схема которого показана на рис. 7.62. Он отличается только тем, что имеет большее число входов /, К. а кроме того, имеет еще асинхронный вход Sd. которым триггер может быть установлен в состояния Q = B, Q=H. На рис. 7.63 показана схема более сложного триггера TTp.L 9000 или TTjiL 9001. Тип 9000 имеет входы /г (показаны пунктиром) без инверторов, а к базам 2 и Г? подключены конденсаторы емкостью 10 пФ. Эти конденсаторы улучшают режим работы в тех случаях, когда начинает сказываться взаимный временной сдвиг тактовых импульсов отдельных триггеров. Но, с другой стороны, они х--X-X-?г  Рис. 7.62. а) У/С-триггер с главной и вспомогательной памятью; б) логическая схема уменьшают частоту переключения триггера, которая равна 20 МГц у типа 9000 и 35 МГц у типа 9001. Триггер имеет по три входа - / и К, один совмещенный вход JK, вход тактовых импульсов ТИ и асинхро1Няые входы Rd и Sd. Инвертирующий усилитель на входе ТИ увеличивает помехоустойчивость этого входа, уменьшает нагрузку источника ТИ и снижает требования, предъявляемые к крутизне фронта и спада ТИ. При уровне В на входе ТИ блокируются входы /, ТС и на состояние главной и вспомогательной памяти могут повлиять только асинхронные входы Rd и Sd. При отрицательном изменении тактового импульса состояние вспомогательной памяти не меняется, и после спада тактового импульса до уровня Н получают преимущество входы J и К в зависимости от состояния выходов вспомогательной памяти. Если Q = B, то имеют преимущество входы К, и, наоборот, если Q = B, то--входы /. Очевидно, что единственная возможность изменения состояния под действием входов J и К при уровне Н на входе ТИ заключается в том, чтобы состояние главной памяти было противоположно состоянию вспомогательной памяти. Состояние главной памяти может изменить только выход конъюнктора, соответствующий входу / или К. при условии, что на всех входах конъюнктора в любой момент времени, когда вход ТИ имеет уровень Н, будет уровень В. При положительном изменении тактового импульса новое состояние главной памяти [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [ 115 ] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0094 |