|

|

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [ 114 ] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] рядится через д7 и коллектор Т,е. При отрицательном изменении напряжения? на входе ТИ через Де проходит отрицательный импульс на базу Tj, который запирается, а значит, запирается и транзистор Тц. Результатом является изменение состояния триггера. Обратим внимание на то, что изменение состояния возможно лишь тогда, когда на выходе Q -уровень Н. При уровне В на выходе-Q Tie остается закрытым, на входе диода Де большое положительное напряжение, поэтому диод остается закрытым и прн отрицательном изменении напряжения на входе ТИ. Очевидно, что при / = /С=ТИ отрицательный импульс проходит через диод Дi или Дв в зависимости от того, на каком выходе триггера имеется уровень Н. Прямой вход iRd активен при уровне Н и устанавливает триггер, в состоянии Q = H, Q = B. Типовая схема / Л-триггера, принцип действия которого основан на использовании заряда, накапливаемого в диодах, представлена на рис. 7.57. Допус-

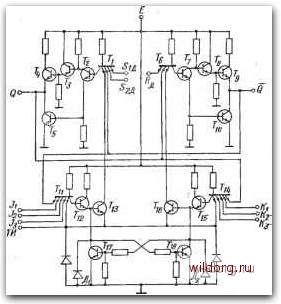

Рис. 7.57. Ж-триггёр с кратковременной полупроводниковой памятью  тим, что q = H, q=B и /=Я=В. После положительного изменения напряжения! входа тактовых импульсов запираются все эмиттеры Тц, через его коллектор начинает протекать ток в базу Т12, и через эмиттер этого транзистора в диоде Д] накапливается заряд, на диоде возникает положительное напряжение. Транзистор 7"i3 не может открыться, потому что на его эмиттере большое напряжение, соответствующее уровню В тактового импульса. Соединенные накрест транзисторы Тп, Тщ представляют простую схему с двумя устойчивыми состояниями. Положительное напряжение диода Дь а значит, и коллектора Тп насыщает транзистор Tie, а небольшое напряжение его» коллектора запирает Тп. Коллектор Тщ соединен с эмиттером Ti5, который заперт, потому что соответствующий эмиттер транзистора Ти соединен с выходом-Q, имеющим уровень Н. При отрицательном изменении напряжения на входе ТИ падает одновременно напряжение и на эмиттерах Т13, Tie и запирается Т. Так как на базе Tis - положительное напряжение диода с накоплением заряда Ди то этот транзистор) открывается, в его коллектор потечет ток от подключенного эмиттера Ti, закрываются транзисторы Тг, Ts и триггер изменяет свое состояние. Аналогично переключается триггер при состоянии входов J к К, как показано в функциональной таблице на рис. 7.576. Так как заряд поступает в диоды Д1 и Дг из: ш.епен с малым сопротивлением, которыми являются эмиттерные повторители Т,2. 15, и так как заряд рассасывается также через малые сопротивления коллекторных цепей и Tis, то триггер может работать на очень высоких частотах, порядка десятков мегагерц. Для установления триггера в исходное состояние используются прямые входы S,d, S2D, iRd, которые активны при уровне Н. Если Sii> = H или S2i) = H, то триггер устанавливается в состояние Q = B, Q = H, в обратное состояние он устанавливается под действием сигнала с уровнем Н на входе Яю- Эти прямые входы влияют на состояние триггера независимо от состояния входа ТИ. На практике используется несколько типов такого триггера, которые отличаются величиной максимальной частоты переключения. Триггер с частотой переключения до 20 МГц имеет бд.р=40 не, зд.р=20 не, =5 не и • = =8 НС. Минимально допустимая длительность тактового импульса - 20 не. В течение этого времени в диоде Д1 или Дг накапливается достаточно большой заряд, обеспечивающий надежную работу триггера и при длительности отрицательного изменения ТИ 100 не. Информация о состоянии входов J w К регистрируется соответствующим ДНЗ, как только напряжение на входе ТИ достигнет 1, 8 В, и передается триггеру только тогда, когда напряжение на входе ТИ упадает до 1,2 В. Надежная работа триггера обеспечена тем, что при этом напряжении уже заблокированы цепи, соответствующие входам J к К. Длительность тактового импульса может быть как угодно большой, поэтому триггер может работать и при очень низких частотах переключения. При положительном изменении напряжения на входе ТИ информация на входах / и /С должна быть уже стабилизирована. Если на входе ТИ есть тактовый импульс, то триггер обнаружит изменение на входах J к К с уровня Н на В в течение 10 не, а с уровня В на Н - в течение 300 не. Так как триггер может переключиться только после достижения определенного порогового напряжения во время отрицательного изменения ТИ, то вход ТИ имеет большую помехоустойчивость уровней В и Н. Этот тип триггера выгодно использовать в синхронных и асинхронных счетчиках и сдвиговых регистрах. У триггера того же типа с частотой переключения до 35 МГц составляет 1.0зд р 25 НС, <<-зд.р=20 кc,t>=4 не, ".ig не „ минимально допустимая длительность тактового импульса-15 не. Для триггера с частотой переключения до 50 МГц, имеющего несколько измененную схему, характерны значения •зд.р=11 НС, эд.р=9 НС, t>=l не, Р-=1,7 не, максимальные значения

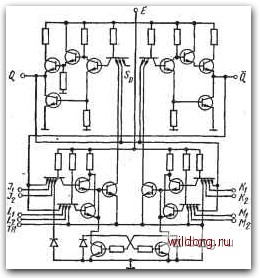

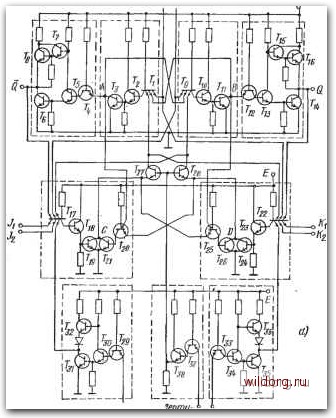

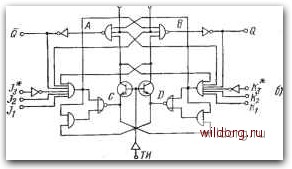

к, К; X... МюВое состояние И илаВ Рис. 7.58. /ТС-триггер с кратковременной полупроводниковой памятью  1,0зд р=<1).1зд,р = 15 НС, /"=2,5 НС, t>=4 НС. Минимально допустимая длительность тактового импульса-10 не. Все представленшзге данные справедливы нри нагрузочных емкостях Си=15 пФ на выходах Q к Q. На этом же принципе работает и триггер на рис. 7.58 с двухуровневой логической функцией на входах J а К в последовательности конъюнкция - Инверсия И-НЕ Од И-НЕ Инверш Е И-ИЛН-НЕ и-или-щ  И-НЕ л иеит 3, рцющий ти tfg усилитель * И-НЕ  Рис. 7.59. а) /ТС-триггер, реагирующий на положительное изменение тактового импульса; б) логическая схема [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [ 114 ] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.009 |

||||||||||||||||||||||||||||||||||||||