|

|

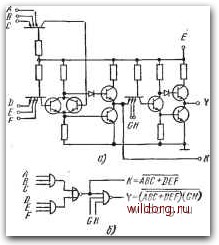

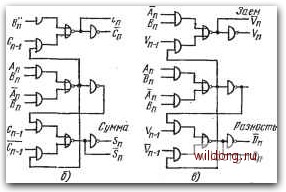

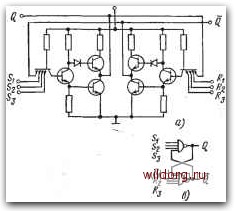

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [ 113 ] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] Использование схем И/ИЛИ-НЕ позволяет во многих случаях разработать-более простую систему, чем на схемах И-НЕ. SNSitSoX Hi Ilk Расшири- r глеш "jt z--i Иг 1,ви -rr>-of R -~- Влияние расширителя на ts MBitho ограничигпьза счет использования внешнего резистора Ri,B нОм Рис. 7.51. а) Схема И/ИЛИ-НЕ с расширителями; б) логическая схема   Рис 7.52. а) Схема И/ИЛИ-НЕ с добавочным инвертором; б) логическая схема На рис. 7.52 показана схема И/ИЛИ-НЕ с добавочным оконечным инвертором, она выполняет функцию ИСКЛЮЧАЮЩЕЕ ИЛИ. Эта схема позволяет упростить составление полных сумматоров и вычитателей (рис. 7.53) АВ+АВ Перенос  Рис. 7.53. а) Пример использования схемы И/ИЛИ-НЕ с .инвертором для создания: б) полного сумматора; в) полного вычитателя ТРИГГЕРЫ ТТЛ В сериях ТТЛ имеются самые разнообразные типы триггеров, работа которых основана на разных принципах. К наиболее распространенным относятся схемы с главной и вспомогательной памятью; схемы со связью по постоянному напряжению, принцип действия которых основан на использовании задержки в полупроводниковых элементах; схемы, использующие полупроводниковые элементы, накапливающие заряд; в меньшей мере используются схемы с емкостны-  S -SfS Bj Рис. 7.54. а) Интегральный ;i?.S-TpHrrep; б) функциональная таблица; в) логическая схема ш ® I-°л

Рис. 7.55. а) Интегральный tRS-tpnrrep, управляемый уровнем тактового импульса; б) функциональная таблица; в) логическая схема ми связями, с точки зрения логической функции наиболее распространены JK-"триггеры, имеющие всестороннее использование, далее £)-триггеры и интегральные -триггеры. i?5 - т р и г г е р ы. На рис. 7.54 представлены схема полного интегрального ?5-триггера и его функциональная таблица. Значение поиятия «неопределенное состояние НО» было объяснено в главе, посвященной асинхронным триггерам. В основе схемы лежат два элемента И-НЕ, от свойств которых зависят и свойства триггера. На рис. 7.55 представлена более сложная схема интегрального /?5-триггера, управляемого уровнем тактового импульса ТИ. Принцип действия ясен из функ-.циональиой таблицы на рис. 7.556, в которой представлены состояния выхода Q в момент t=n+l после ТИ в зависимости от состояний управляющих входов в момент i=n перед ТИ. Функция входов Sc и Яп такая же, как у простого J?S-tphrrepa на рис. 7.54. / ТС - т р и г г е р ы. Схема интегрального триггера на рис. 4.56 состоит из i 1 1 /Г» 1 X

Рис. 7.56. Ж-триггер с емкостной связью входа ТИ двух элементов - И-НЕ - и сравнительно сложных входных ключей, которые позволяют достигать частоты пере11<лючения порядка 30 МГц. Рассмотрим работу ключа на входе состоящего из двух простых схем ТТЛ на транзисторах Tj-Tis. Другими интегральными элементами являются диоды Дъ - Дв и конденсаторы Cj, Сг. Предположим, что триггер находится в состоянии Q = H, Q = B и что на входах / и ТИ - уровень Н. Конденсатор Ci быстро заряжается через Тп, Tis, Де, и навходе Дь возникает большое положительное напряжение. Так как на входе / уровень Н, то через эмиттер T,s протекает ток на вход /, и Гш заперт. При положительном изменении напряжения на входе ТИ появляется положительный импульс на входе Дв, который еще больше -запирает этот диод. При отрицательном изменении напряжения на входе ТИ на входе Дв появляется отрицательный импульс, который, однако, не попадает на •базу Т-,, потому что Де заперт большим положительным напряжением. Допустим теперь, что на входе / - уровень В. В этом случае закрывается лереход эмиттер - база 7"i5, ток коллектора которого проходит в базу Т;. В коллектор Tie- течет ток эмиттера Тп, транзистор 7"i8 заперт, и на входе Де имеется только небольшое положительное напряжение. При положительном изменении напряжения на входе ТИ Дв закроется и конденсатор Ci быстро раз- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [ 113 ] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0125 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||