|

|

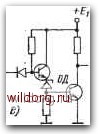

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [ 10 ] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] t-ax+fi-" на уровень Н, как это показано на рис. 1.266. После задержки /н,. вызванной иэбыточны-м зарядом, .накопленным в схеме В, находившейся в на---сыщенлом состоянии, выход схемы будет уже иметь уровень В. Таким образом, состояние схеыы В указывает на неправильную работу схемы А по исте- ,у-т нГв)  индинацил изменений свтвйяий  -----г„-V-А-----ог Вход Выход J Рис. 1.26. а) Принцип определения предела кратковременных помех; б) сигнал на выходе при воздействии на вход положительного импульса номех; в) отрицательного импульса помех чеиии времени а мнни.мальная ширина 1полож1ительного импульса :помех, который может быть обнаружен, равна н„„„=4а(1.10) Рассмотрим теперь искажение уровня В схемы А. Уровни, соответствующие нормальному состоянию, представлены на рис. 1.26а в скобках. Предположим, что на входной уровень В схемы А воздействует идеальный отрицательный импульс, вызывающий изменение уровня выхода схемы А иа уровень Н по истечении времени /н--/*-. В этом случае представляет задержку, связанную с наличие,ч избыточного заряда в насыщенной схеме А. Минимальная обнаруживаемая ширина отрицательного .импульса помех равна = + (1.П> В обоих случаях влияние импульса помех определяется так, что при данной амплитуде этого импульса измеряется его минимальная длительность, при которой отмечается измененне состояния схемы А. Частота повторения импульсов (1.12) зд +l- + tB-Ti Зависимость ширины импульса от его амплитуды может 5ыть выражена следующими соотношениями: Нмин - Вмин = г + н > (1.14) где Ян, Кв-постоянные, зависящие от параметров схемы н напряжения источника питания, а /н, /в - амплитуды сигналов помех. Из представленных (Соотношений вытекает, что 1;редел допустимых кратков.ременных помех цкфро-шой схемы зависит от произведения амплитуды и ширины импульса помех, т. е. от его энергии. Обратим также вни.мание на взаимную связь между шириной импульса помех и увеличением времени распространения схемы. Согласно рнс. 1.26в имеем: HMHH=4ip+0,5f-°, Вмин = ад!р + 05°. Так как для схем с большим быстродействием справедливы 0,5t•<t>sR.t, .и 0,5t><Р-д.р, то получим: Нмин" 1.0 зд.р , (1.15) (1.16) неравенства (1.17) Искажение ровня И \ искажение уроВнлВ  f /0,1 Вмин зд.р и. М .11-J tsf.p, ср - Предел йпютчес-ких помех ijpadw Н Рис. 1.27. Типичные пределы кратковременных помех (1.18) Из этих соотношений вытекает, что на правильную работу схемы не окажут влияния положительные импульсы помех, длительность которых меньше задержки -зд.р, а амплитуда не превышает уровня В, и отрицательные импульсы помех с длительностью, меньшей задержки -зд.р, и амплитудой, которая не упадет ниже уровня Н. Другими словами, чем меньше быстродействие схемы, тем она более устойчива к воздействиям кратковременных импульсов помех. Типичные пределы допустимых кратковременных помех представлены на рис 1.27. С одной стороны, они асимптотически приближаются к пределу допустимых статических помех, а с другой стороны, достигают теоретически ббоко1неч1ного значения для случая очень коротких импульсов. Представленные принципы могут быть применены н для цепочек схем в самых тяжелых рабочих условиях. К кратковременным помехам очень чувствительны схемы с емкостной входной связью. Влияние помех в зависимости от величины пороговых уровней цифровой схемы Допустимые пределы искажений, особенно уровня Н, зависят от величины порогового уровня Т. У схем с большим напряжением питания диапазон изменения цифрового сигнала больше и больше пороговый уровень Т, при котором схема меняет свое состояние. Казалось бы, поэтому такие схемы, имея большие пределы напряжений статических помех, менее чувствительны к помехам. Однако влияние помех значительно сложнее. Из соображний уменьшения мощности потерь схемы с большим напряжением питания должны иметь большие входнме и выходные сопротивления. Но прн этом увеличивается влияние емкостных связей, которые приводят к большим помехам на входал схем. Поэтому выбор большего порогового уровня имеет смысл прежде всего с точки зрения уменьшения влияния помех, возникающих на заземлениях и проводах, подводящих напряжение питания, так как схемы с большими и малыми напряжениями питания рассчитываются приблизительно на одинаковые токн. У схемы с маленьким напряжением питания при таком же токе, как в схемах с большим напряжением питания, пороговое напряженке меньше, поэтому меньше и пределы статических помех, но прн этом уменьшаются также входное н выходное сопротивления, а значит, ,и влияние емкостных связей. Очень маленькое выходное сопротивление в состоянии В особенно характерно для схем с активным выходом. У интегральных схем с маленьким напряжением питания - от -ЬЗ до -f5 В--пороговый уровень Т можно увеличить путем последовательного включения большого числа переходов пассивных или активных полупроводниковых элементов. Примеры таких включений показаны на рис. 1.28а-г. Наименьший щ -J-  Рис. 1.28. а) Схема с минимальным входным пороговым уровнем; б) увеличение порогового уровня с помощью смещающих диодов Дем; в) с помощью перехода эмиттер - база транзистора Ti и диода Д; г) с помощью переходов эмиттер - база транзисторов Ti и Гг; д), е) с помощью опорного диода пороговый уровень (порядка 0,6-0,7 В) имеет схема типа РТЛ да рис. 1.28а. В схеме типа ДТЛ на рис. 1.286 диоды Дом позволяют увеличить пороговый уровень примерно до 1,5 В. Такой же пороговый уровень .имеют схемы на рис. 1.28в и г. На рис. 1.28в один из диодов Дом заменен переходом эмиттер-база транзистора Ti, а на рис. 1.28г оба диода Дом заменены переходами эмиттер-база Ti и Ti. На рис. 1.28д и е приведены примеры увеличения порогового уровня с помощью опорного диода, .используемые в интегральных схемах с напряжением питания £i=10-f-20 В. Пороговый уровень этих схем 5-7 В, и 111ри.мерно такой же величины допустимые пределы статических помех. В некоторых случаях для эффективного подавления влияния помех могут быть использованы специальные схе.мы с гистерезисной передаточной характеристикой. Для сравнения на рис. 1.29а изображена идеализированная передаточная характеристика инвертирующей схемы без гистерезиса, а на рис. 1.296 - идеализированная передаточная характеристика инвертирующей схемы с отрицательным гистерезисом. С ростом входного напряжения от уровня Н выход [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [ 10 ] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0182 |