|

|

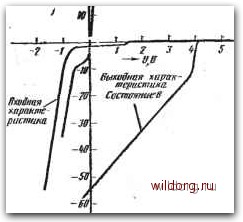

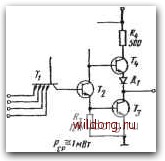

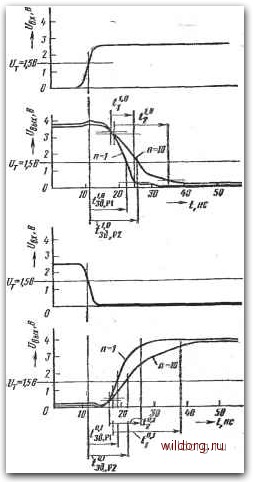

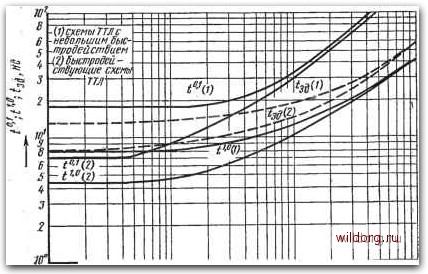

Главная страница Систематические методы минимизации [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [ 107 ] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] «а линейна, выход схемы можно считать генератором тока. Для представленных предельных зяаченвй выходного тока короткого замыкания выходное сопротивление будет (Ом) « -f" ~ 0 - 150 Ом. (7.26) В области больших выходных иапряжений и малых токов Та и Т» работают в АКТИВНОЙ области и выходное сопротивление падает до величины ?вых «/?а/Р(т.) Р(Т.). (7-27) значение которой порядка 30 Ом. Некоторые статические характеристики показаны на рис. 7.29. Рассмотренные схемы с составным транзистором на выходе используются не только в качестве бьктро-действующих схем ТТЛ, «о представляют основу схем с малым быстродействием, Мощных схем ТТЛ с большими выходными токами. уОнлвЗная корактеришма Состояние н  <и гокЦ  Рис. 7.30. Схема ТТЛ с очень малой мощностью по-Рис. 7.29. Статические характеристики герь СХЕМЫ ТТЛ С МАЛОЙ МОЩНОСТЬЮ ПОТЕРЬ Типичная схема ТТЛ с малой мощностью потерь представлена на рис. 7.30. Сопротивления резисторов Mt и 7?2, которые, в принципе, определяют среднюю мощность потерь, в 10 раз больше, чем у стандартной схемы ТТЛ на рис. 7.8а, поэтому мощность потерь составляет около 1 мВт. Статические характеристики подобны, но их диапазон тока почти в 10 раз меньше. Несмотря на то что схема имеет по сравнению со стандартной схемой ТТЛ в 10 раз меньшую мощность потерь, она отличается сравнительно большим быстродействием, потому что среднее время задержки всего лишь в 3 раза больше. Поэтому схема очень устойчива к динамическши помехам. Во время работы схемы имеют место очень •малые изиенения тока в проводах, подводящих питание, и в заземлении. Поэтому помехи, генерируемые схемой, малы. С точки зрения надежности имеет большое значение низкая рабочая температура активных полупроводниковых элементов схемы. Тепловое сопротивление перехода корпус - окружающая сре- да типовой ИС составляет 0,2°/мВт. Таким образом, совыестиое включение десяти стандартных схем ТТЛ прн общей мощности потерь 100 мВт ииеет температуру перехода на 20°С выше по сравнению с окружающей средой. В такой же системе из десяти схем ТТЛ, имеющих общую мощность потерь 10 мВт, температура перехода возрастет только на 2° С по сравнению с окружающей средой. Поэтому схемы ТТЛ с очень малой мощностью потерь пригодаы ие только-для систем с большой плотностью элементов и минимальной исщностью потерь,, но и для систем, от которых требуется большая надежность, без требования: обеспечения минимальной мощности потерь и потребляемой мощности. ВРЕМЯ ПЕРЕКЛЮЧЕНИЯ И ЗАДЕРЖКИ СИгалЛОВ Значения этих характеристических величин зависят от рабочих условий схемы, прежде всего от емкостной нагрузки выхода. Емкостную нагрузку представляют уже сами входы .следующих схем ТТЛ, подключенных к выходу. Каждый вход .нагружает выход емкостью, величина которой в зависимости от типа схемы колеблется в пределах от 1 до нескольких пикофаград. При полной нагрузке выхода, например десятью входами следующих схем (и =,10), результирующая емкостная нагрузка может достигать нескольких десятков пикофарад и увеличит время переключения и задержку сигнала. На рис. 7.31 показаны примеры .изменения выходных сигналов при минимальной нагрузке выхода п=1 и при максимальной нагрузке .выхода и=10. С увеличением числа единичных нагрузок увеличивается время переключения .и задержка. Значительно большее влияние на величину задержки оказывают длинные .соединения «ли линии, нагруженные таким большим сопротивлением, что они, в пр.инци-пе, работают в режиме холостого хода и представляют собой емкостную нагрузку. Зависимость времени переключения п задержки от общей нагрузочной е.мкостн Св показана на рис. 7.32. При зарядке этих емкостей на выходе схемы ТТЛ могут иметь место сравнительно большие зарядные токи. Если, например, Сн=20 пФ и перепад выходного сигнала AU= =3 В, то иа выходе быстродействующей схемы ТТЛ в течение Af=5 нс не будет тока заряда -(мА):  , = С„ =20 = 12. At 5 (7.28) Рис. 7.31. Напряжение на выходе схемы ТТЛ: а) при изменении с уровня В яа Н; б) при изменении с уровня Н аа В При Сн=100 пФ и Л<=10 НС 4=30 мА. Эти токи влияют на мощность потерь и потребляемую мощность схем ТТЛ. Они не должны вызывать появление недопустимо больших сигналов помех в подводящих питание проводах и заземлении. В схемах ТТЛ с большим быстродействием должно быть обращено внимание на неиспользованные входы. Как показано на рис. 7.33а, неподключенный вход эмиттера имеет по отношению к земле определенную емкость. При отрицательном изменении напряжения на входе А с уровня В на Н изменяется также напряжение на неподключенном входе В. При положительном же изменении напряжения на входе А с уровня Н на В конденсатор С заряжается через сопротивление Я базы входного транзистора Т-и пока напряжение на конденсаторе С  10" 2 3 и 5 618310 г 3 4 5618310 2 3 U 5 S 78310 Рис. 7.32. Пример зависимости времени переключения и задержки схемы ТТЛ от величины емкости нагрузки ие достигнет достаточной величины, Г] не реагирует на положительное иэмене-1ние напряжения на входе А. Это замедляет работу всей схемы ТТЛ. Ограничение влияния неиспользуемых входов может быть решено двумя способами. Первый способ заключается в том, что неиспользуемые входы подключаются к достаточно большему положительному напряжению, которое обеспечивает запирание соответствующих эмиттеров. Согласно рис. 7.336 эти входы могут быть подключены прямо к источнику питания Е. Если есть опасность пробоя, то входы должны быть подключены к источнику напряжения Е через ограничительный резистор с сопротивлением 1- 5 кОм, как на рис. 7.33в. Неиспользуемые входы могут быть без ограннчитель-«ого сопротивления подключены к особому источнику напряжения, которое будет меньше Е, но этот метод более дорогостоящий. Второе способ заключается в подключении неиспользуемых входов к Используемым так, как показано на 5)ис. 7.33г. Емкости неиспользуемых входов в этом случае разряжаются и заряжаются прямо через выходы управляющих схем. Ток, протекающий через все соединенные входы в состоянии Н, представляет одну единичную нагрузку выхода управляющей схемы. В схеме на рис. 7.33а каждый невйлючениый вход увеличивает задержку •зд.р примерно на 1 не. Другими факторами, влияющими на время яереключенпя и задержку, являются напряжение питания и температура окружающей среды. Схемы ТТЛ [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [ 107 ] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] 0.0107 |