|

|

Главная страница Мультиплексирование цифровых сигналов [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [ 11 ] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] Рис. 2.19 иллюстрирует процесс считывания адреса коммутации из ЗУ, который управляет считыванием информации из речевых ЗУПВ. Этот адрес вырабатывается управляющими устройствами АТС по полученному номеру вызывающего и номеру вызываемого абонентов. Адреса коммутации (адреса считывания) из управляющего ЗУ SWCM

к ЗУПВ1и ЗУПВ2 к ЗУПВЗ и ЗУПВ4 Длительность кодового слова (3,9 мкс) СР80 1 Jl nJl ri rLrLrLrLr TLnj-LTLr ос 11 "L 1 J" Моменты f считывания i n n r t" t Рис. 2.19. Считывание адреса коммутации ВА - адрес записи/считывания, СР80 - тактовый сигнал 8,192 МГц, ОС - выбор адреса записи/считывания, CPL - разрешение считывания адреса В табл. 2.3 указан порядок считывания адресов коммутации. Например, если необходимо установить соединение, при котором данное кодовое слово должно быть передано в заданном временном канальном интервале в четвертую исходящую ИКМ линию, то считывание будет производиться в момент /=16 согласно адресу коммутации, содержащемуся в селекторе адреса 2 (этот адрес указывает, в какой ячейке ЗУПВ записаны 8 бит кодового слова заданной входящей ИКМ линии). Таблица 2.3. Порядок считывания адресов коммутации

Считанные из ЗУПВ кодовые слова подаются в регистры передачи (рис. 2.20), а затем в преобразователи p/s. Запись и считывание в регистры приема, ЗУПВ и в регистры передачи. как правило, разнесены во времени таким образом, чтобы не возникало блокировок при записи/считывании (см. табл. 2.2-2.4). от ЗУПВ 1 и ЗУПВ2 от ЗУПВЗ и ЗУПВ4

Длительность кодового слова (3,9 мкс) СР80 • JTJlJn mnJ~LrLri ri П П Г1 П Г r-L i-Lr-Lr~L f ,t f t f Рис. 2.20. Порядок передачи ИКМ слов в преобразователь p/s Таблица 2.4. Порядок передачи адресов коммутации

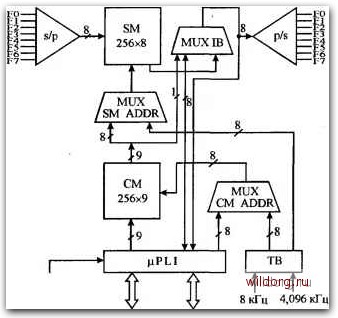

2. Использование мультиплексоров и демулыпиплексоров Примером такого подхода в построении S/Т-ступенк является БИС, разработанная итальянскими специалистами для цифровой системы PROTEL UT и получившая название интегрального коммутационного элемента (ECI). ECI является ЖТ-ступенью с параметрами S/T: (8/32)х(8/32). Микросхема ЕС1 может прямо подключаться к шине 8-битового процессора и является для него стандартным периферийным устройством. На рис. 2.21 показана ее структурная схема. В схеме ECI можно выделить следующие функциональные блоки: синхронизирующее устройство (ТВ); преобразователи последовательного кода ИКМ кодового слова в параллельный и наоборот (s/p и p/s); речевое ЗУ (SM); управляющее ЗУ (СМ); логический интерфейс микропроцессора (pPLI); мультиплексоры (мультиплексор адреса управляющей памяти - MUX SM ADDR, мультиплексор внутренней ИКМ шины - MUX IB, мультиплексор адреса речевой памяти - MUX СМ ADDR). Синхронюирующее устройство ТВ генерирует и формирует все необходимые синхронизирующие сигналы, используя два внешних сигнала - 4 кГц и 4,096 МГц. В частности, устройство задает два счетчика (входной и выходной) для преобразователей s/p и p/s. Кроме того, из синхросигнала 4 кГц схема ТВ задает три счетчика: СТ1, СТ2 и СТЗ.  AIA2S1S2 от (к) микропроцессора Рис. 2.21. Структурная схема ECI Первый счетчик (СТ1) формирует отсчет длительности одного канального интервала (примерно 4 мкс). Второй и третий счетчики (СТ2 и СТЗ) работают синхронно со счетчиком СТ1 и вырабатывают последовательные канальные адреса для чтения из управляющего ЗУ и записи в речевое ЗУ соответственно. Речевое ЗУ организовано в виде 8 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру бита в кодовом слове, каждая строка - номеру канального интервала в структуре цикла ИКМ-30, а каждый столбец - номеру входящей ИКМ линии. Рабочий цикл ЗУ (около 4 мкс) - разделен на два подынтервала по 2 мкс каждый. Первый подинтервал содержит восемь циклов длительностью 250 не каждый. В первом цикле в речевое ЗУ записываются по соответствующим адресам 8 бит из каждой линии ИКМ-30. Остальные циклы используются для связи с логическим интерфейсом микропроцессора и приема адреса считывания из управляющего ЗУ. Во втором подинтервале осуществляется считывание 8 бит кодовых слов согласно адресам, полученным из управляющего ЗУ. Управляющее ЗУ имеет 9 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру канального интервала в структуре цикла ИКМ-30 (одно поле для проверочных бит). Адреса записаны в управляющем ЗУ так же, как и в речевом. Рабочий цикл управляющего ЗУ организован аналогично рабочему циклу речевого ЗУ. Во время первого подинтервала ЗУ связано с микропроцессором для получения управляющих сигналов. Во втором подинтервале по сигналам счетчиков СТ1 и СТ2 восемь раз про- [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [ 11 ] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] 0.0107 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||