|

|

Главная страница Классификация стабилизирующих источников [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [ 42 ] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] 133ТМ2) и дешифратора на логических элементах ЗИ (DDs... ... DD12). Выходы дешифратора соединены со вторыми информационными входами мультиплексора на логических элементах 2И-2ИЛИ-НЕ (DD13...DD16) и 2И-НЕ (DD17... DD20). Первые информационные входы мультиплексора соединены с вводами импульсов внешнего управления {U\, U2, U3, U4).

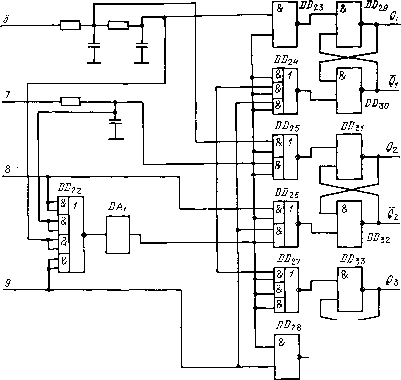

Рис. 2.31. Узел логической обработки импульсов управления Вход управления мультиплексора (объединенные входы И логических элементов DD13... DDie) через логический элемент 2И-НЕ {DD21) подключен ко входу Up команды режима работы. Автогенератор DAi вырабатывает последовательность импульсов заданной частоты. При подаче на вход режима работы Up Положительного потенциала напряжения 2,4... 5 В разрешается прохождение тактовых импульсов на счетчик DD3... DD4, с выхода которого подаются на вход дешифратора DDs... DDg перепады Напряжения по заданной программе. При этом на объединенные Входы И дешифратора DDs DDg подаются импульсы автогенератора, которые в определенной последовательности по заданной программе выделяются на выходах дешифратора и поступают на 5-90 129 вторые информационные входы мультиплексора. На выходе инвертора DD21 в это время нулевой потенциал, который запрещает прохождение импульсов внешнего управления на выход мультиплексора. На выходе мультиплексора импульсы управления переключением задаются по программе узла АФК. При подаче на вход С/р нулевого потенциала блокируется прохождение импульсов автогенератора на вход дешифратора, а на выходе узла АФК (С/выхь [/вых 2, [/выхз, [/вых 4) выделяются импульсы внешнего управления. С выхода узла АФК импульсы управления подаются на входы [/вхь [/вх2, [/вхз, [/вх4 узла логической обработки импульсов управления (рис. 2.31), содержащего три /?5-триггера на логических элементах 2И-НЕ {DD29... DD34), два логических элемента 2И-НЕ {DD23, DDis), выход первого из которых подключен к 5-входу .5-триггера высшей ступени {DD29, DD30), а выход второго -к /?-входу триггера низшей ступени {DD33, DD34), /?-вход триггере высшей ступени подключен к выходу логического элементе 2И-ЗИЛИ-НЕ (DDia), а 5-вход триггера низшей ступени - к вы ходу логического элемента 2И-ЗИЛИ-НЕ {DDzj), R- и 5-входь триггера третьей ступени напряжения подключены соответствен но к выходам логических элементов 2И-2ИЛИ-НЕ (DD25, D-D26) Один из входов И логических элементов 2И {DD23... DD23) объ единены с выходом ждущего мультивибратора DA2, вход которо го подключен к выходу логического элемента 4ИЛИ-НЕ, входь последнего соединены с выходами мультиплексора непосредствен, но или через элементы задержки, выполненные на /?С-цепочках ВВ-, Ч тх ВВ,. i ВВ вв< Рис. 2.32. Схема распределения и формирования импульсов 130 при использовании в качестве разрядных и зарядных ключевых элементов транзисторов, соединенных по схеме на рис. 2.25, блок управления (рис. 2.31) дополняется узлом распределения и формирования импульсов, показанным на рис. 2.32. Узел содержит генератор тактовых импульсов Аи вырабатывающий последовательность импульсов с частотой порядка 200 кГц и скважностью 2, которые через логические элементы 2И-НЕ {DD4... DDe) поступают на вход импульсных усилителей Лг... At и через логические элементы ЗИ-НЕ (Ds... -D10) на вход импульсных усилителей Аб... As. Выходы импульсных усилителей А ... А, принципиальная электрическая схема которых показана на рис. 2.33, соединяются с переходами база-эмиттер зарядных транзисторов (см. рис. 2.25), а выходы импульсных усилителей Ае... Аа соединяются с переходами база - эмиттер разрядных транзисторов. Ждущий мультивибратор As формирует импульс напряжения длительностью, несколько большей времени разряда емкости нагрузки, который включает разрядные транзисторы на заданное Бремя. Поддержание транзисторов разрядных и зарядных элементов во включенном состоянии осуществляется пакетом импульсов, длительность которого определяется командой блока управления (рис. 2.31), где Qi, Qj, q3 - соответствующие прямые выходы RS-триггеров, а Qi, q2, q3 - инверсные выходы этих триггеров. Ждущий мультивибратор запускается по любой из команд на переключение уровня выходного напряжения и вырабатывает импульс напряжения длительностью порядка 25 мкс, который запрещает на это время формирование следующего импульса на выходе блока управления. Этим обеспечивается невозможность переключения уровней с частотой, большей 4 кГц. I- I с VII Рис. 2.33. Схема импульсных усилителей [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [ 42 ] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] 0.0119 |

||||||||||